参数资料

| 型号: | IP-SDRAM/DDR2 |

| 厂商: | Altera |

| 文件页数: | 64/106页 |

| 文件大小: | 0K |

| 描述: | IP DDR2 SDRAM CONTROLLER |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | DDR2 SDRAM 控制器 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页当前第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

�� �

�

�

�3–28�

�Chapter� 3:� Functional� Description�

�Interfaces� &� Signals�

�Signals�

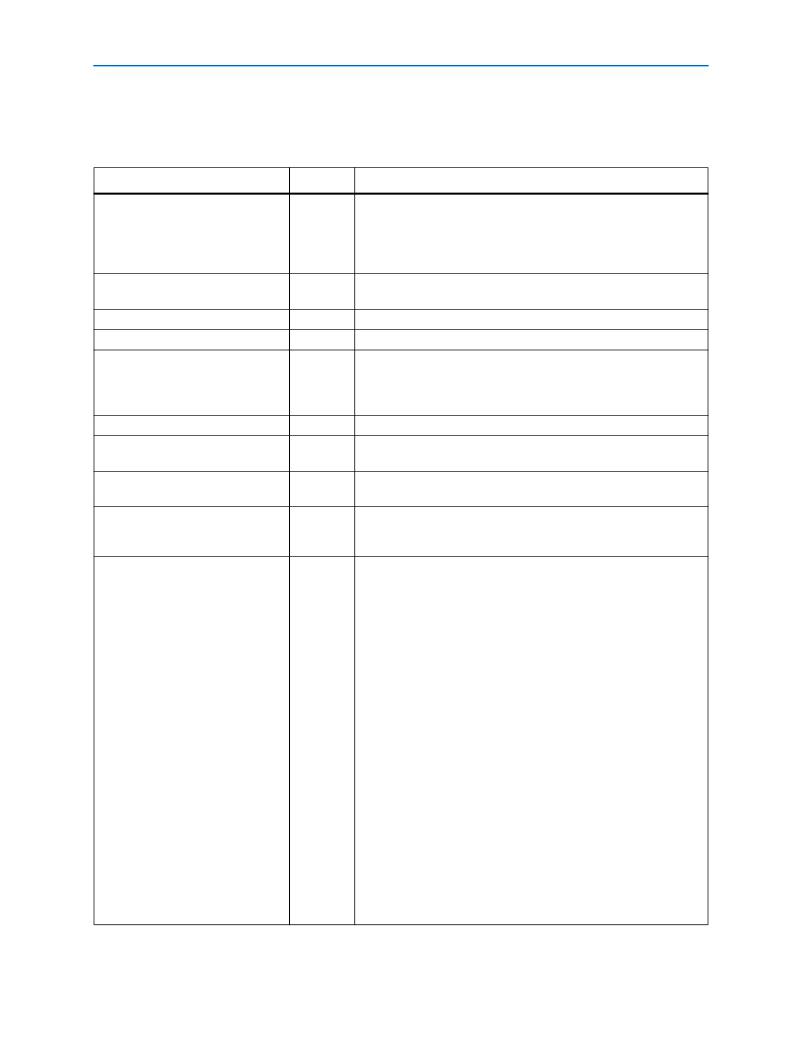

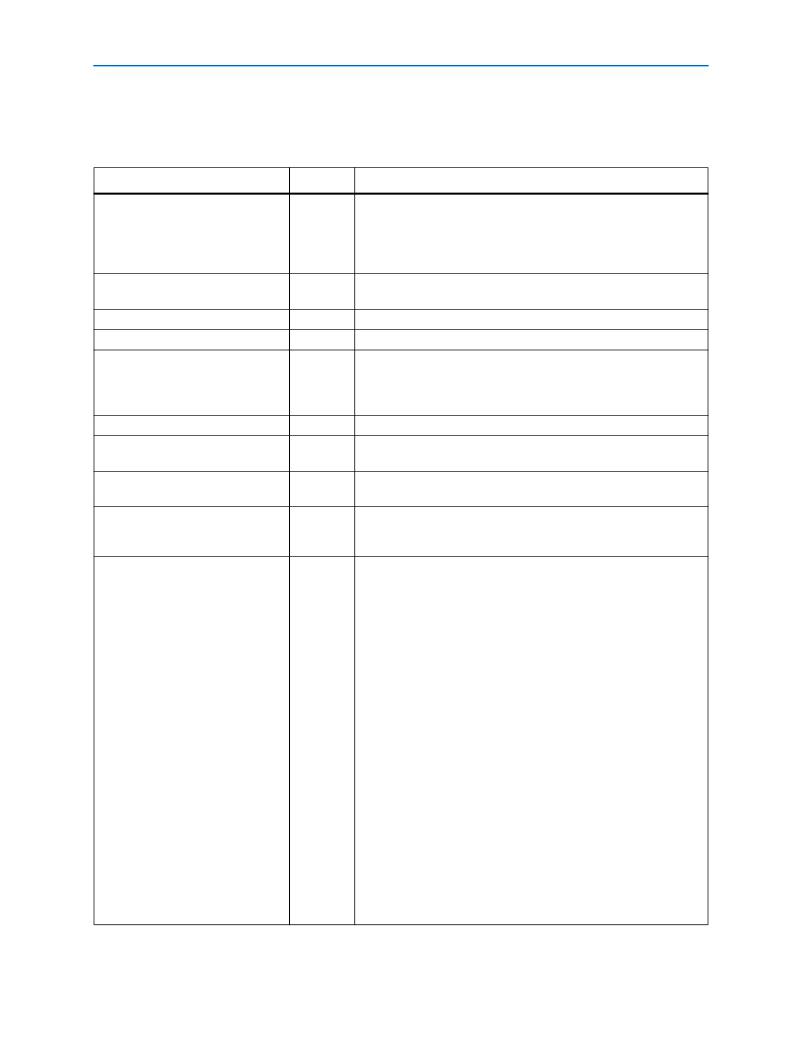

��Table� 3–7.� System� Signals� (Part� 1� of� 2)�

�Signal� Name�

�addrcmd_clk�

�capture_clk�

�clk�

�dqs_delay_ctrl[5:0]�

�dqsupdate�

�fedback_clock_in�

�postamble_clk� (1)�

�reset_n�

�resynch_clk� (1)�

�resynch_clk_edge_select�

�Direction�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Input�

�Description�

�The� clock� to� the� address� and� command� output� registers.� Only�

�available� if� Insert� extra� pipeline� registers� in� the� datapath� is� on.� The�

�addrcmd_clk� signal� allows� you� to� adjust� the� address� and�

�command� output� timing,� if� required.� The� addrcmd_clk� signal� is�

�connected� to� the� system� clock� by� default.�

�Optional� clock� that� can� be� used� instead� of� DQS� to� capture� read� data,�

�for� example� in� the� Stratix� side� banks.�

�System� clock.�

�Control� bus� from� the� DLL� to� the� DQS� pins.�

�The� Stratix� II� DLL� generates� the� dqsupdate� signal� for� the� DQS� pins� to�

�control� when� the� DQS� delay� chain� value� can� update.� Only� available� if�

�the� interface� is� on� a� single� side� of� the� device� and� Insert� logic� to� allow�

�the� DLL� to� update� during� the� memory� refresh� period� is� off.�

�Fed-back� clock� input.�

�The� postamble� logic� clock,� which� disables� the� capture� registers� before�

�the� end� of� the� DQS� read� postamble� period.�

�System� reset,� which� can� be� asserted� asynchronously� but� must� be�

�deasserted� synchronous� to� the� rising� edge� of� the� system� clock.�

�Clock� that� resynchronizes� read� data� from� the� DQS� clock� domain� to� the�

�system� clock� domain.� Typically,� you� can� use� the� system� clock� as� the�

�resynchronization� clock.�

�Allows� you� to� switch� on� a� second� pair� of� registers,� clocked� on� the�

�negative� edge� of� the� resynchronization� clock,� immediately� after� the�

�resynchronization� registers.� This� feature� allows� safer� transfer� of� your�

�resynchronized� read� data� back� to� the� system� clock� domain,� if� your�

�resynchronization� clock� phase� is� variable.� It� is� only� available� in�

�designs� targetting� a� HardCopy� II� device� or� if� a� HardCopy� II� device� is�

�specified� as� a� companion� device� in� your� project.� By� default,� the�

�example� design� connects� the� signal� to� logic� zero,� which� disables� the�

�extra� set� of� registers.�

�The� resynch_clk_edge_select� is� added� to� HardCopy� II�

�designs� to� allow� you� to� safely� adjust� the� resynchronization� clock� while�

�still� maintaining� a� safe� transfer� back� to� the� system� clock� domain.� An�

�extra� set� of� resynchronization� registers� are� inserted� on� the� opposite�

�edge� and� a� multiplexer� to� select� which� register's� output� to� pass� on� to�

�the� system� clock� register� (refer� to� Figure� 3–19� ).�

�The� output� of� the� capture� register� goes� to� the� resynchronization�

�register,� which� may� be� clocked� on� the� rising� edge� of� a� dedicated� PLL�

�output.� The� extra� logic� (a� falling� edge� register� and� a� multiplexer)� gets�

�inserted� before� the� system� clock� register.�

�You� should� keep� this� select� signal� programmable� if� your�

�resynchronization� clock� phase� can� be� tuned� by� the� PLL�

�reconfiguration� block.� If� you� tie� it� off� to� a� fixed� value,� you� may� limit� the�

�range� across� which� you� can� adjust� your� resynchronization� clock.�

��?� March� 2009� Altera� Corporation�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP-SLITE2 | IP SERIALLITE II |

| IP-SRAM/QDRII | IP QDRII SRAM CONTROLLER |

| IP-VITERBI/SS | IP VITERBI LOW-SPEED |

| IP4220CZ6,125 | IC USB DUAL ESD PROTECT 6TSOP |

| IPA-66-1-600-10.0-A-01-T | CIRC BRKR 10A 2POLE SCREW TERM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPSE.4.33SM600 | 制造商:Banner Engineering 功能描述:FIBER IPSE.4.33SM600 GLASS FIBER (MIN ORDER 50) |

| IPSE.4.62SM600 | 制造商:Banner Engineering 功能描述:FIBER IPSE.4.62SM600 GLASS FIBER (MIN ORDER 50) |

| IPS-EMBEDDED | 功能描述:开发软件 Embedded IP Suite MegaCore RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPS-EVAL-EH-01 | 功能描述:ENERGY HARVESTING BOARD RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:THINERGY® 标准包装:1 系列:- 主要目的:数字电位器 嵌入式:- 已用 IC / 零件:AD5258 主要属性:- 次要属性:- 已供物品:板 相关产品:AD5258BRMZ1-ND - IC POT DGTL I2C1K 64P 10MSOPAD5258BRMZ10-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ100-ND - IC POT DGTL I2C 100K 64P 10MSOPAD5258BRMZ50-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ1-R7-ND - IC POT DGTL I2C 1K 64P 10MSOPAD5258BRMZ10-R7-ND - IC POT DGTL I2C 10K 64P 10MSOPAD5258BRMZ50-R7-ND - IC POT DGTL I2C 50K 64P 10MSOPAD5258BRMZ100-R7-ND - IC POT DGTL I2C 100K 64P 10MSOP |

| IPS-EVAL-EH-02 | 制造商:Infinite Power Solutions 功能描述:BOARD EVAL WIRELESS SENSING |

发布紧急采购,3分钟左右您将得到回复。