- 您现在的位置:买卖IC网 > PDF目录1987 > AD9547BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9547BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 37/104页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9547 Mask Change 20/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750kHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页当前第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

AD9547

Data Sheet

Rev. E | Page 38 of 104

2×

÷N

VCO

CALIBRATION

LOCK

DETECT

SYSTEM

CLOCK

÷M

LOOP

FILTER

SYSCLKN

SYSCLKP

SYSCLK_VREG

SYSCLK_LF

HF

XTAL

LF

34

37

38

35

PFD

AND

CHARGE

PUMP

08300-

020

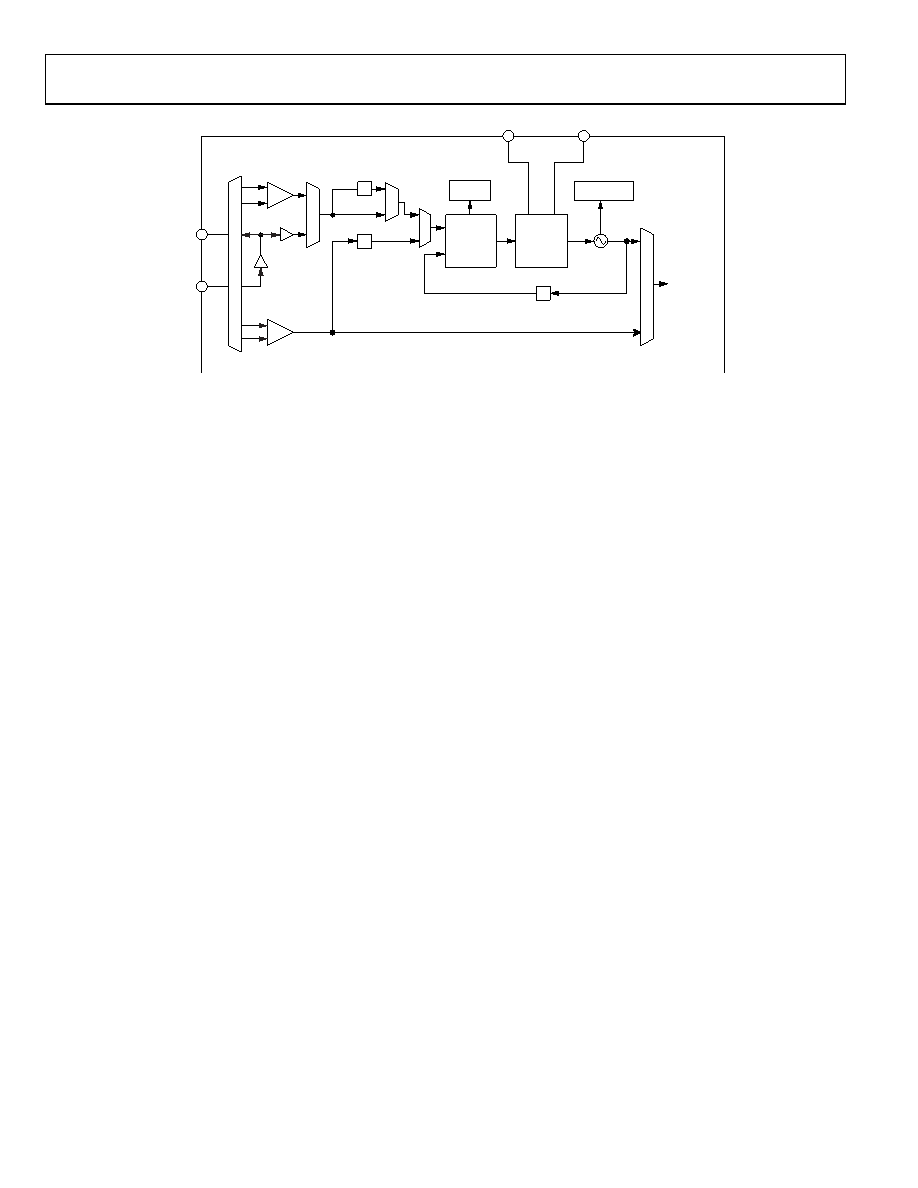

Figure 44. System Clock Block Diagram

The LF path permits the user to provide an LVPECL, LVDS,

CMOS, or sinusoidal low frequency clock for multiplication

by the integrated SYSCLK PLL. The LF path handles input

frequencies from 3.5 MHz up to 100 MHz. However, when

using a sinusoidal input signal, it is best to use a frequency in

excess of 20 MHz. Otherwise, the resulting low slew rate can

lead to substandard noise performance. Note that the LF path

includes an optional 2× frequency multiplier to double the rate

at the input to the SYSCLK PLL and potentially reduce the PLL

in-band noise. However, to avoid exceeding the maximum PFD

rate of 150 MHz, use of the 2× frequency multiplier is valid only

for input frequencies below 125 MHz.

The XTAL path enables the connection of a crystal resonator

(typically 10 MHz to 50 MHz) across the SYSCLKx input pins.

An internal amplifier provides the negative resistance required

to induce oscillation. The internal amplifier expects a 3.2 mm ×

2.5 mm AT cut, fundamental mode crystal with a maximum

motional resistance of 100 Ω. The following crystals, listed in

alphabetical order, may meet these criteria. Note that, although

these crystals meet the preceding criteria according to their data

sheets, Analog Devices, Inc., does not guarantee their operation

with the AD9547, nor does Analog Devices endorse one crystal

manufacturer/supplier over another.

AVX/Kyocera CX3225SB

ECS ECX-32

Epson/Toyocom TSX-3225

NDK NX3225SA

Siward SX-3225

SYSCLK PLL MULTIPLIER

The SYSCLK PLL multiplier is an integer-N design and relies on

an integrated LC tank and VCO. It provides a means to convert

a low frequency clock input to the desired system clock frequency,

fS (900 MHz to 1 GHz). The SYSCLK PLL multiplier accepts input

signals between 3.5 MHz and 500 MHz, but frequencies in excess

of 150 MHz require the M-divider to ensure compliance with

the maximum PFD rate (150 MHz). The PLL contains a feedback

divider (N) that is programmable for divide values between 6 and

255. The nominal VCO gain is 70 MHz/V.

Lock Detector

The SYSCLK PLL has a built-in lock detector. Register 0x0100,

Bit 2 determines whether the lock detector is active. When it

is active (default), the user controls the sensitivity of the lock

detector via the lock detect divider bits (Register 0x0100, Bits[1:0]).

Note that a value of zero must be written to the system clock

stability timer (Register 0x0106 to Register 0x0108) whenever

the lock detector is disabled (Register 0x0100, Bit 2 = 1).

The SYSCLK PLL phase detector operates at the PFD rate, which is

fVCO/N. Each PFD sample indicates whether the reference and feed-

back signals are phase aligned (within a certain threshold range).

While the PLL is in the process of acquiring a lock condition,

the PFD samples typically consist of an arbitrary sequence of

in-phase and out-of-phase indications. As the PLL approaches

complete phase lock, the number of consecutive in-phase PFD

samples grows larger. Thus, one way of indicating a locked

condition is to count the number of consecutive in-phase PFD

samples and, if it exceeds a certain value, declare the PLL locked.

This is exactly the role of the lock detect divider bits. When the

lock detector is enabled (Register 0x0100, Bit 2 = 0), the lock detect

divider bits determine the number of consecutive in-phase

decisions that are required (128, 256, 512, or 1024) before the lock

detector declares a locked condition. The default setting is 128.

Charge Pump

The charge pump operates in either automatic or manual mode,

based on the charge pump mode bit (Register 0x0100, Bit 6).

When Register 0x0100, Bit 6 = 0, the AD9547 automatically selects

the appropriate charge pump current based on the N divider value.

Note that the user does not have control of the charge pump cur-

rent bits (Register 0x0100, Bits[5:3]) in automatic mode. When

Register 0x0100, Bit 6 = 1, the user determines the charge pump

current via the charge pump current bits (Register 0x0100,

相关PDF资料 |

PDF描述 |

|---|---|

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| AD9549ABCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9548 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad/Octal Input Network Clock Generator/Synchronizer |

| AD9548/PCBZ | 功能描述:BOARD EVAL FOR AD9548 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9548/PCBZ | 制造商:Analog Devices 功能描述:Clock Generator Evaluation Board |

| AD9548BCPZ | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9548BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。