- 您现在的位置:买卖IC网 > PDF目录1987 > AD9547BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9547BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 76/104页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9547 Mask Change 20/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750kHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页当前第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

Data Sheet

AD9547

Rev. E | Page 73 of 104

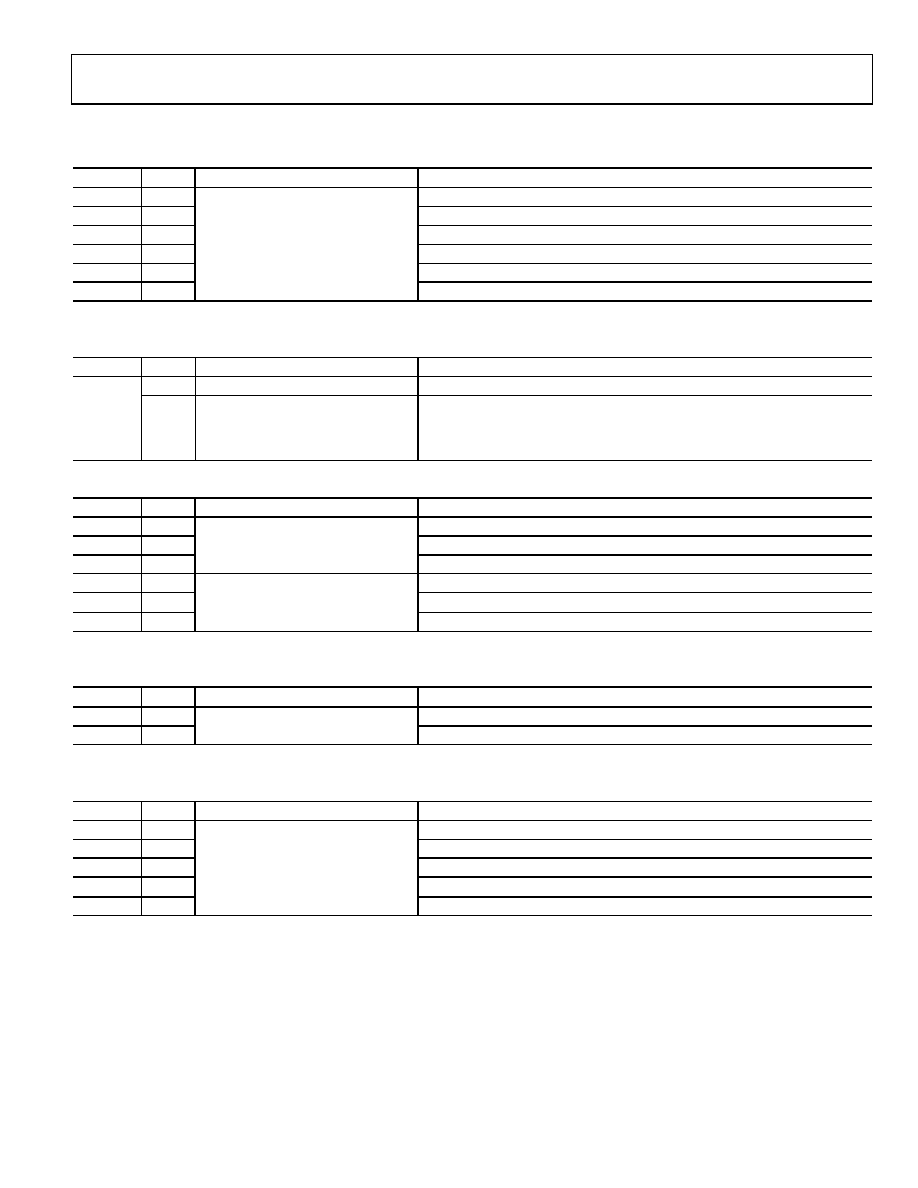

DPLL CONFIGURATION (REGISTER 0x0300 TO REGISTER 0x031B)

Table 58. Free-Running Frequency Tuning Word1

Address

Bit

Bit Name

Description

0x0300

[7:0]

Free-running frequency tuning word

(expressedas a 48-bit frequency

tuning word)

Free-running frequency tuning word, Bits[7:0].

0x0301

[7:0]

Free-running frequency tuning word, Bits[15:8].

0x0302

[7:0]

Free-running frequency tuning word, Bits[23:16].

0x0303

[7:0]

Free-running frequency tuning word, Bits[31:24].

0x0304

[7:0]

Free-running frequency tuning word, Bits[39:32].

0x0305

[7:0]

Free-running frequency tuning word, Bits[47:40].

1

The default free-running tuning word is 0x000000= 0, which equates to 0 Hz.

Table 59. Update TW

Address

Bit

Bit Name

Description

0x0306

[7:1]

Unused

Unused.

0

Update TW

A Logic 1 writtento this bit transfers the free-running frequency tuning word

(Register 0x0300 to Register 0x0305) to the register embeddedinthe tuning

word processinglogic. Note that it is not necessary to write the update TW bit

when the device is in free-run mode. This is an autoclearing bit.

Table 60. Pull-in RangeLower and Upper Limit1

Address

Bit

Bit Name

Description

0x0307

[7:0]

Pull-inrange lower limit (expressed

as a 24-bit frequency tuning word)

Lower limit pull-inrange, Bits[7:0].

0x0308

[7:0]

Lower limit pull-inrange, Bits[15:8].

0x0309

[7:0]

Lower limit pull-inrange, Bits[23:16].

0x030A

[7:0]

Pull-inrange upper limit (expressed

as a 24-bit frequency tuning word)

Upper limit pull-inrange, Bits[7:0].

0x030B

[7:0]

Upper limit pull-inrange, Bits[15:8].

0x030C

[7:0]

Upper limit pull-inrange, Bits[23:16].

1

The default pull-in range lower limit is 0 and the upper range limit is 0xFFFFFF, which effectively spans the full output frequency range of the DDS.

Table 61. Open-Loop Phase Offset1

Address

Bit

Bit Name

Description

0x030D

[7:0]

Open-loop phase offset

(expressedinunitsofπ/215 radians)

DDS phase offset, Bits[7:0].

0x030E

[7:0]

DDS phase offset, Bits[15:8].

1

The default DDS phase offset is 0.

Table 62. Fixed Closed-Loop Phase Lock Offset1

Address

Bit

Bit Name

Description

0x030F

[7:0]

Fixedphase lock offset

(expressedin ps)

Fixedphase lock offset, Bits[7:0].

0x0310

[7:0]

Fixedphase lock offset, Bits[15:8].

0x0311

[7:0]

Fixedphase lock offset, Bits[23:16].

0x0312

[7:0]

Fixedphase lock offset, Bits[31:24].

0x0313

[7:0]

Fixedphase lock offset, Bits[39:32].

1

The default fixed closed loop phase lock offset is 0.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| AD9549ABCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9548 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad/Octal Input Network Clock Generator/Synchronizer |

| AD9548/PCBZ | 功能描述:BOARD EVAL FOR AD9548 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9548/PCBZ | 制造商:Analog Devices 功能描述:Clock Generator Evaluation Board |

| AD9548BCPZ | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9548BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。