- 您现在的位置:买卖IC网 > PDF目录1987 > AD9547BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9547BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 48/104页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9547 Mask Change 20/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750kHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页当前第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

AD9547

Data Sheet

Rev. E | Page 48 of 104

Note that conditional processing is applicable only when down-

loading (see the EEPROM Conditional Processing section).

Automatic EEPROM Download

Following power-up, assertion of the RESET pin, or a soft reset

(Register 0x0000, Bit 5 = 1), if FncInit[7:3] ≠ 0 (see the Initial M0

to M7 Pin Programming section), the instruction sequence stored

in the EEPROM executes automatically with condition =

FncInit[7:3]. In this way, a previously stored set of register values

downloads automatically on power-up or with a hard or soft

reset. See the EEPROM Conditional Processing section for

details regarding conditional processing and the way that it

modifies the down-load process.

EEPROM Conditional Processing

The condition instructions allow conditional execution of

EEPROM instructions during a download sequence. During

an upload sequence, however, they are stored as is and have

no effect on the upload process.

Note that, during EEPROM downloads, the condition instructions

themselves and the end instruction always execute unconditionally.

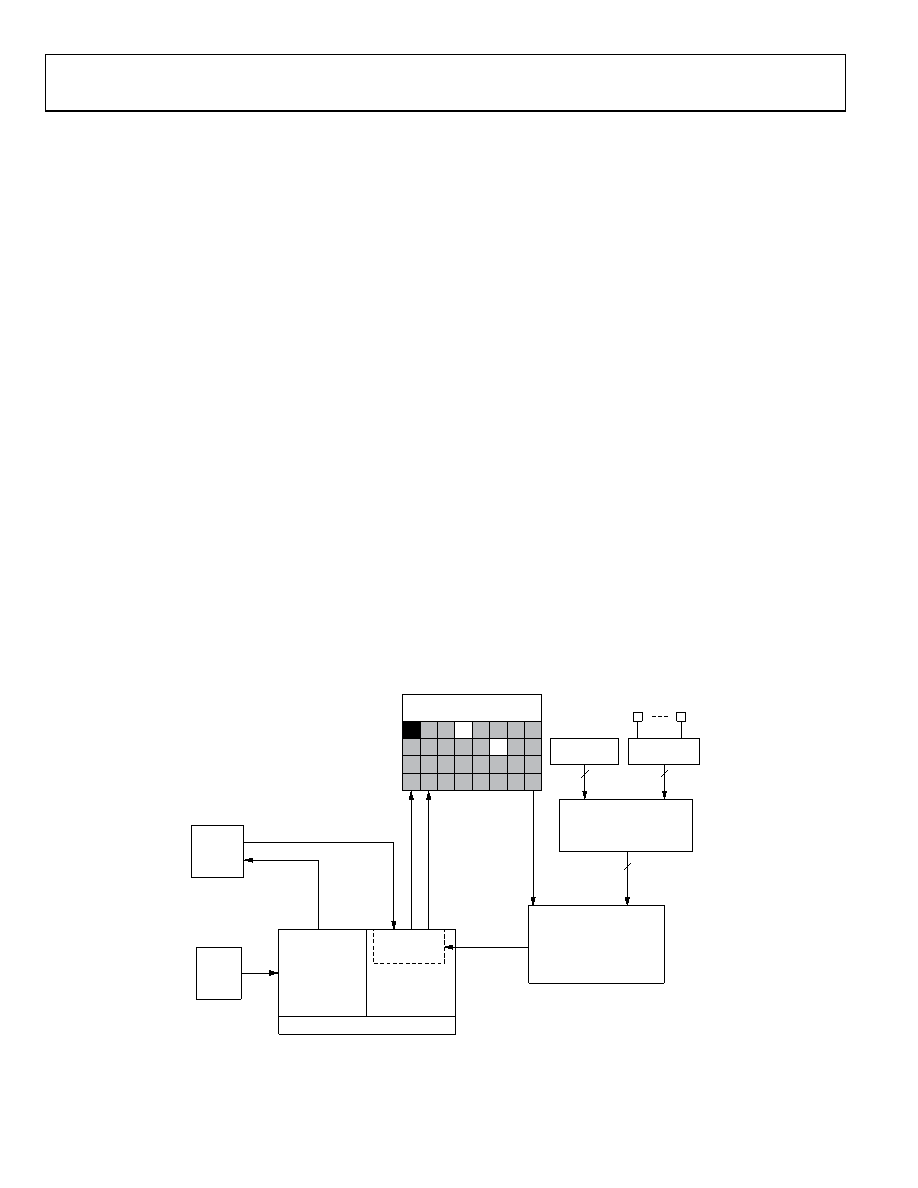

Conditional processing makes use of two elements: the condition

(from Condition 1 to Condition 31) and the condition tag board.

The relationships among the condition, the condition tag board,

and the EEPROM controller appear schematically in Figure 49.

Condition is a 5-bit value with 32 possibilities. Condition = 0 is the

null condition. When the null condition is in effect, the EEPROM

controller executes all instructions unconditionally. The remaining

31 possibilities, condition = 1 through condition = 31, modify the

EEPROM controller’s handling of a download sequence.

The condition originates from one of two sources (see Figure 49),

as follows:

FncInit, Bits[7:3], which is the state of multifunction pins

M3 to M7 at power-up (see the Initial M0 to M7 Pin

Programming section)

Register 0x0E01, Bits[4:0]

If Register 0x0E01, Bits[4:0] ≠ 0, then the condition is the value

stored in Register 0x0E01, Bits[4:0]; otherwise, the condition is

FncInit, Bits[7:3]. Note that a nonzero condition that is present

in Register 0x0E01, Bits[4:0] takes precedence over FncInit,

Bits[7:3].

The condition tag board is a table that is maintained by the

EEPROM controller. When the controller encounters a condition

instruction, it decodes Condition Instruction 0xB1 through Condi-

tion Instruction 0xCF as condition = 1 through condition = 31,

respectively, and tags that particular condition in the condition

tag board. However, Condition Instruction 0xB0 decodes as the

null condition, for which the controller clears the condition tag

board; subsequent download instructions execute unconditionally

(until the controller encounters a new condition instruction).

During download, the EEPROM controller executes or skips

instructions, depending on the value of the condition and the

contents of the condition tag board. Note, however, that condition

instructions and the end instruction always execute uncondi-

tionally during download. If condition = 0, all instructions during

download execute unconditionally. If condition ≠ 0 and there

are any tagged conditions in the condition tag board, the controller

executes instructions only if the condition is tagged.

EXAMPLE

CONDITION 3 AND

CONDITION 13

ARE TAGGED

EEPROM

EEPROM CONTROLLER

UPLOAD

PROCEDURE

CONDITION

HANDLER

DOWNLOAD

PROCEDURE

CONDITION

TAG BOARD

1

6

5

4

3

2

11

10

9

8

7

30

31

24

23

22

21

20

19

18

17

16

15

14

13

12

25

26

27

28

29

IF B1 ≤ INSTRUCTION ≤ CF,

THEN TAG DECODED CONDITION

EXECUTE/SKIP

INSTRUCTION(S)

SCRATCH

PAD

CONDITION

CONDITION = 0x0E01, BITS[4:0]

ELSE

CONDITION = FncInit, BITS[7:3]

ENDIF

M7

M3

IF INSTRUCTION = B0,

THEN CLEAR ALL TAGS

FncInit, BITS[7:3]

REGISTER

0x0E01, BITS[4:0]

STORE CONDITION

INSTRUCTIONS AS

THEY ARE READ FROM

THE SCRATCH PAD.

WATCH FOR

OCCURRENCE OF

CONDITION

INSTRUCTIONS

DURING

DOWNLOAD.

IF {NO TAGS} OR {CONDITION = 0}

EXECUTE INSTRUCTIONS

ELSE

IF {CONDITION IS TAGGED}

EXECUTE INSTRUCTIONS

ELSE

SKIP INSTRUCTIONS

ENDIF

5

IF {0x0E01, BITS[4:0] ≠ 0}

Figure 49. EEPROM Conditional Processing

相关PDF资料 |

PDF描述 |

|---|---|

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| AD9549ABCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9548 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad/Octal Input Network Clock Generator/Synchronizer |

| AD9548/PCBZ | 功能描述:BOARD EVAL FOR AD9548 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9548/PCBZ | 制造商:Analog Devices 功能描述:Clock Generator Evaluation Board |

| AD9548BCPZ | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9548BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。