- 您现在的位置:买卖IC网 > PDF目录1987 > AD9547BCPZ-REEL7 (Analog Devices Inc)IC CLOCK GEN/SYNCHRONIZR 64LFCSP PDF资料下载

参数资料

| 型号: | AD9547BCPZ-REEL7 |

| 厂商: | Analog Devices Inc |

| 文件页数: | 44/104页 |

| 文件大小: | 0K |

| 描述: | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| 产品变化通告: | AD9547 Mask Change 20/Oct/2010 |

| 标准包装: | 750 |

| 类型: | 时钟/频率发生器,同步器 |

| PLL: | 是 |

| 主要目的: | 以太网,SONET/SDH,Stratum |

| 输入: | CMOS,LVDS,LVPECL |

| 输出: | CMOS,LVDS,LVPECL |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:2 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 750kHz |

| 电源电压: | 1.71 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 64-VFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 64-LFCSP-VQ(9x9) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页当前第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页

AD9547

Data Sheet

Rev. E | Page 44 of 104

STATUS AND CONTROL

MULTIFUNCTION PINS (M0 TO M7)

The AD9547 has eight digital CMOS I/O pins (M0 toM7) that are

configurable for a variety of uses. The function of these pins is

programmable via the register map. Each pin can controlor moni-

tor an assortment of internal functions, based on the contents of

Register 0x0200 to Register 0x0207. To monitor an internal

function with a multifunction pin, write a Logic 1 to the MSB

of the register associated with the desired multifunction pin. The

value of the seven LSBs of the register defines the control function,

as shown in Table 25.

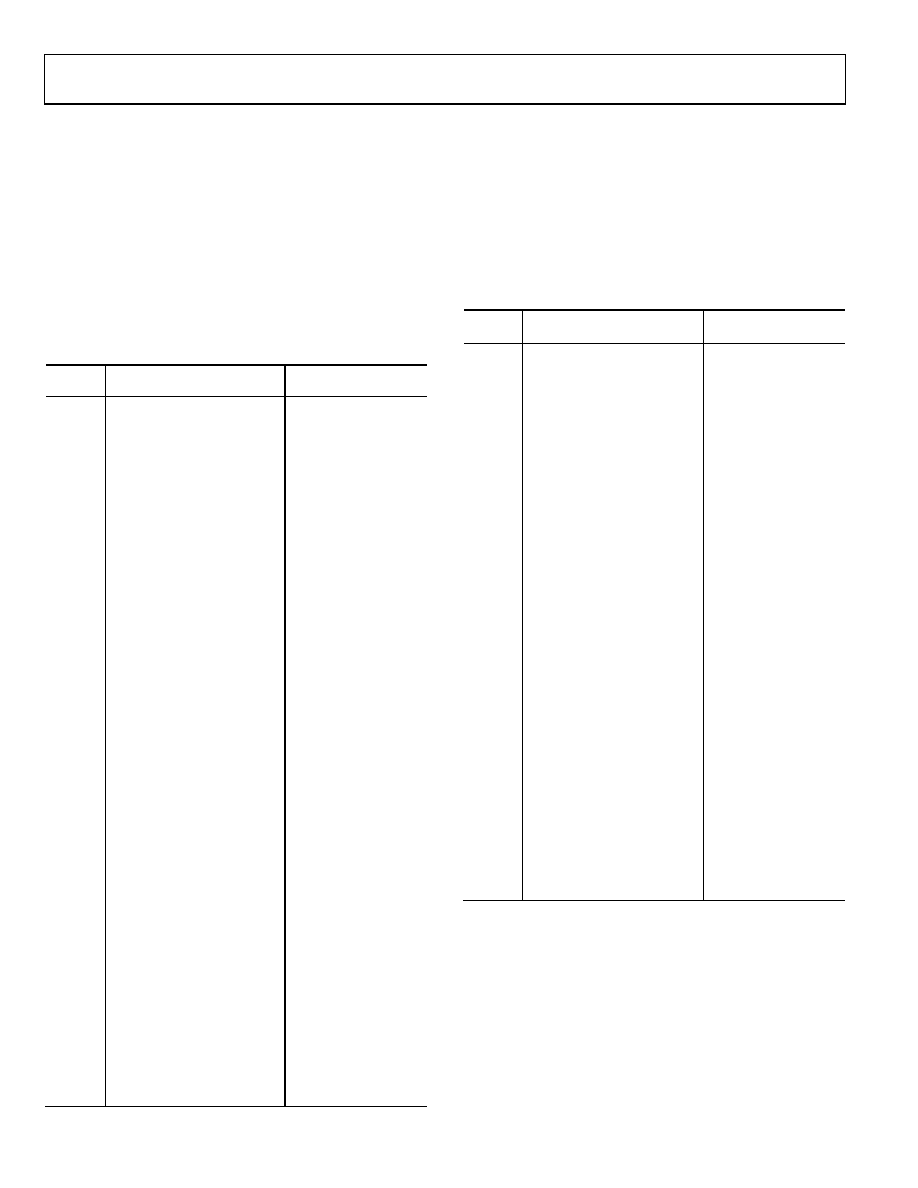

Table 25. Multifunction PinOutput Functions (D7 = 1)

D[6:0]

Value

Output Function

Source Proxy

0

Static Logic 0

1

Static Logic 1

2

System clock divided by 32

3

Watchdog timer output

4

EEPROM upload in progress

Register 0x0D00, Bit 0

5

EEPROM download in progress

Register 0x0D00, Bit 1

6

EEPROM fault detected

Register 0x0D00, Bit 2

7

SYSCLK PLL lock detected

Register 0x0D01, Bit 0

8

SYSCLK PLL calibration in progress

Register 0x0D01, Bit 1

9

Unused

10

Unused

11

SYSCLK PLL stable

Register 0x0D01, Bit 4

12 to 15

Unused

16

DPLL free running

Register 0x0D0A,Bit 0

17

DPLL active

Register 0x0D0A,Bit 1

18

DPLL in holdover

Register 0x0D0A,Bit 2

19

DPLL in reference switchover

Register 0x0D0A,Bit 3

20

Active reference:phase master

Register 0x0D0A,Bit 6

21

DPLL phase locked

Register 0x0D0A,Bit 4

22

DPLL frequency locked

Register 0x0D0A,Bit 5

23

DPLL phase slew limited

Register 0x0D0A,Bit 7

24

DPLL frequency clamped

Register 0x0D0B,Bit 7

25

Tuning word history available

Register 0x0D0B,Bit 6

26

Tuning word history updated

Register 0x0D05, Bit 4

27 to 31

Unused

32

Reference A fault

Register 0x0D0C, Bit 2

33

Reference AA fault

Register 0x0D0D, Bit 2

34

Reference B fault

Register 0x0D0E, Bit 2

35

Reference BB fault

Register 0x0D0F, Bit 2

36 to 47

Unused

48

Reference A valid

Register 0x0D0C, Bit 3

49

Reference AA valid

Register 0x0D0D, Bit 3

50

Reference B valid

Register 0x0D0E, Bit 3

51

Reference BB valid

Register 0x0D0F, Bit 3

52 to 63

Unused

64

Reference A active reference

Register 0x0D0B,Bits[1:0]

65

Reference AA active reference

Register 0x0D0B,Bits[1:0}

66

Reference B active reference

Register 0x0D0B,Bits[1:0]

67

Reference BB active reference

Register 0x0D0B,Bits[1:0]

68 to 79

Unused

80

Clock distribution sync pulse

Register 0x0D03, Bit 3

81 to

127

Unused

To control an internal function with a multifunction pin, write a

Logic 0 to the most significant bit of the register associated with

the desired multifunction pin. The monitored function depends

on the value of the seven least significant bits of the register, as

shown in Table 26. Note that the default setting is M0 through

M7 configured as inputs and the input function set to unused

(the first entry in Table 26).

Table 26. Multifunction PinInput Functions (D7 = 0)

D[6:0]

Value

Input Function

Destination Proxy

0

Unused (default)

Unused

1

I/O update

Register 0x0005, Bit 0

2

Full power-down

Register 0x0A00, Bit 0

3

Watchdog reset

Register 0x0A03, Bit 0

4

IRQ reset

Register 0x0A03, Bit 1

5

Tuning word history reset

Register 0x0A03, Bit 2

6 to 15

Unused

16

Holdover

Register 0x0A01, Bit 6

17

Free run

Register 0x0A01, Bit 5

18

Reset incremental phase offset

Register 0x0A0C, Bit 2

19

Increment incremental phase

offset

Register 0x0A0C, Bit 0

20

Decrement incremental phase

offset

Register 0x0A0C, Bit 1

21 to 31

Unused

32

Override ReferenceMonitorA

Register 0x0A0F, Bit 0

33

Override ReferenceMonitorAA

Register 0x0A0F, Bit 1

34

Override ReferenceMonitorB

Register 0x0A0F, Bit 2

35

Override ReferenceMonitorBB

Register 0x0A0F, Bit 3

36 to 47

Unused

48

Force Validation Timeout A

Register 0x0A0E, Bit 0

49

Force Validation Timeout AA

Register 0x0A0E, Bit 1

50

Force Validation Timeout B

Register 0x0A0E, Bit 2

51

Force Validation Timeout BB

Register 0x0A0E, Bit 3

52 to 63

Unused

64

Enable OUT0

Register 0x0401, Bit 0

65

Enable OUT1

Register 0x0401, Bit 1

66, 67

Unused

68

Enable OUT0, OUT1

Register0x0401, Bits[1:0]

69

Sync clock distribution outputs

Register 0x0A02, Bit 1

70 to

127

Unused

If more than one multifunction pin operates on the same control

signal, then internal priority logic ensures that only one multi-

function pin serves as the signal source. The selected pin is the

one with the lowest numeric suffix. For example, if both M3

and M7 operate on the same control signal, M3 is used as the

signal source and the redundant pin is ignored.

相关PDF资料 |

PDF描述 |

|---|---|

| AD9548BCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 88LFCSP |

| AD9549ABCPZ-REEL7 | IC CLOCK GEN/SYNCHRONIZR 64LFCSP |

| AD9550BCPZ-REEL7 | IC INTEGER-N TRANSLATOR 32-LFCSP |

| AD9551BCPZ | IC CLOCK GEN MULTISERV 40-LFCSP |

| AD9552BCPZ-REEL7 | IC PLL CLOCK GEN LP 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| AD9548 | 制造商:AD 制造商全称:Analog Devices 功能描述:Quad/Octal Input Network Clock Generator/Synchronizer |

| AD9548/PCBZ | 功能描述:BOARD EVAL FOR AD9548 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| AD9548/PCBZ | 制造商:Analog Devices 功能描述:Clock Generator Evaluation Board |

| AD9548BCPZ | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1 系列:- 类型:时钟/频率发生器,多路复用器 PLL:是 主要目的:存储器,RDRAM 输入:晶体 输出:LVCMOS 电路数:1 比率 - 输入:输出:1:2 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3 V ~ 3.6 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-TSSOP(0.173",4.40mm 宽) 供应商设备封装:16-TSSOP 包装:Digi-Reel® 其它名称:296-6719-6 |

| AD9548BCPZ-REEL7 | 功能描述:IC CLOCK GEN/SYNCHRONIZR 88LFCSP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:28 系列:- 类型:时钟/频率发生器 PLL:是 主要目的:Intel CPU 服务器 输入:时钟 输出:LVCMOS 电路数:1 比率 - 输入:输出:3:22 差分 - 输入:输出:无/是 频率 - 最大:400MHz 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 85°C 安装类型:表面贴装 封装/外壳:64-TFSOP (0.240",6.10mm 宽) 供应商设备封装:64-TSSOP 包装:管件 |

发布紧急采购,3分钟左右您将得到回复。