参数资料

| 型号: | ADP1046ACPZ-RL |

| 厂商: | Analog Devices Inc |

| 文件页数: | 74/92页 |

| 文件大小: | 0K |

| 描述: | IC DGTL CTRLR 32LFCSP |

| 标准包装: | 5,000 |

| 应用: | 电源 |

| 输入电压: | 0 V ~ 1.6 V |

| 电源电压: | 3 V ~ 3.6 V |

| 电流 - 电源: | 20mA |

| 工作温度: | -40°C ~ 125°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-WFQFN 裸露焊盘,CSP |

| 供应商设备封装: | 32-LFCSP-WQ(5x5) |

| 包装: | 带卷 (TR) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页当前第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页

�� �

�

�

�ADP1046�

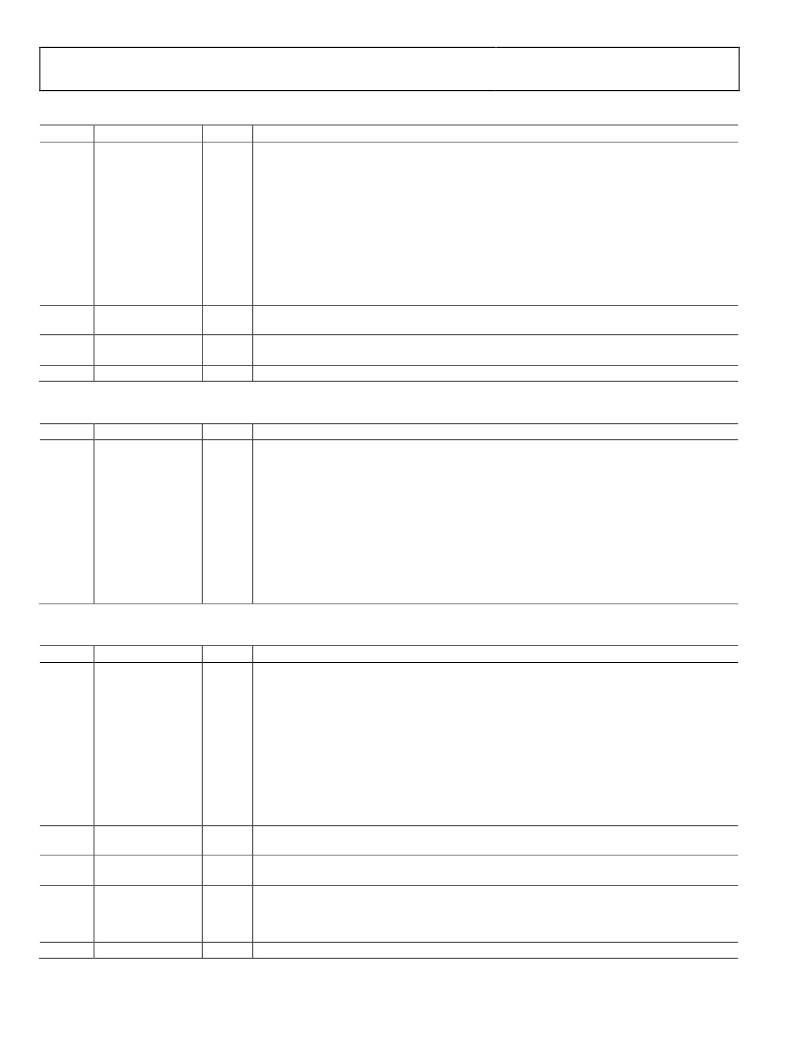

�Table� 90.� Register� 0x5A—OUTAUX� Rising� Edge� Setting� (OUTAUX� Pin)�

�Data� Sheet�

�Bits�

�[7:4]�

�Bit� Name�

�t� 13�

�R/W�

�R/W�

�Description�

�These� bits� contain� the� four� LSBs� of� the� 12-bit� t� 13� time.� This� value� is� always� used� with� the� eight�

�bits� of� Register� 0x59,� which� contains� the� eight� MSBs� of� the� t� 13� time.� Each� LSB� corresponds� to� 5� ns�

�resolution.� The� entire� switching� period� is� divided� into� 40� ns� time� steps.� If� the� t_rise� and� t_fall� of� a�

�PWM� edge� occur� within� the� same� 40� ns� time� step,� the� PWM� output� is� 0� V.� If� the� t_rise� and� t_fall�

�occur� in� different� 40� ns� time� steps,� the� PWM� output� is� set� to� the� programmed� value.� The� absolute�

�maximum� pulse� width� is� t� PERIOD� ?� 5� ns.� Depending� on� the� switching� frequency� and� the� OUTAUX�

�frequency,� there� is� a� constant� lag/lead� time� between� this� edge� and� the� other� edges� (t� 1� to� t� 12� );� there-�

�fore,� OUTAUX� is� not� synchronized� to� the� other� PWM� outputs� but� can� be� made� synchronous� by�

�adjusting� the� delay� accordingly.� If� either� the� OUTAUX� switching� frequency� (Register� 0x3F)� or� the�

�PWM� switching� frequency� (Register� 0x40)� is� changed� after� edge� adjustment,� the� synchronization�

�between� OUTAUX� and� the� PWM� edges� is� no� longer� maintained.� The� OUTAUX� delay� must� be�

�adjusted again to synchronize the edges to the PWM edges for the new set of switching frequencies.�

�3�

�Modulate� enable�

�R/W�

�1� =� PWM� modulation� acts� on� the� t� 13� edge.�

�0� =� no� PWM� modulation� of� the� t� 13� edge.�

�2�

�t� 13� sign�

�R/W�

�1� =� negative� sign.� Increase� of� PWM� modulation� moves� t� 13� right.�

�0� =� positive� sign.� Increase� of� PWM� modulation� moves� t� 13� left.�

�[1:0]�

�Reserved�

�R/W�

�Reserved.�

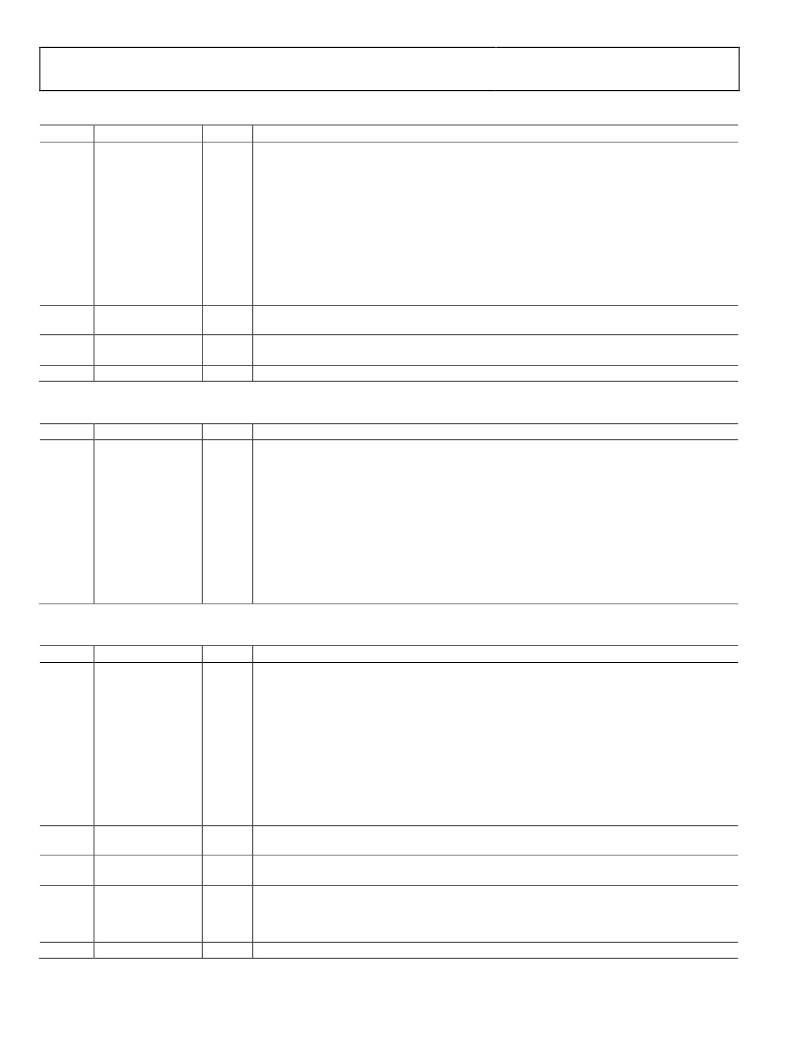

�Table� 91.� Register� 0x5B—OUTAUX� Falling� Edge� Timing� (OUTAUX� Pin)�

�Bits�

�[7:0]�

�Bit� Name�

�t� 14�

�R/W�

�R/W�

�Description�

�This� register� contains� the� eight� MSBs� of� the� 12-bit� t� 14� time.� This� value� is� always� used� with� the� top�

�four� bits� of� Register� 0x5C,� which� contains� the� four� LSBs� of� the� t� 14� time.� Each� LSB� corresponds� to�

�5� ns� resolution.� The� entire� switching� period� is� divided� into� 40� ns� time� steps.� If� the� t_rise� and� t_fall� of�

�a� PWM� edge� occur� within� the� same� 40� ns� time� step,� the� PWM� output� is� 0� V.� If� the� t_rise� and� t_fall�

�occur� in� different� 40� ns� time� steps,� the� PWM� output� is� set� to� the� programmed� value.� The� absolute�

�maximum� pulse� width� is� t� PERIOD� ?� 5� ns.� Depending� on� the� switching� frequency� and� the� OUTAUX�

�frequency,� there� is� a� constant� lag/lead� time� between� this� edge� and� the� other� edges� (t� 1� to� t� 12� );� there-�

�fore,� OUTAUX� is� not� synchronized� to� the� other� PWM� outputs� but� can� be� made� synchronous� by�

�adjusting� the� delay� accordingly.� If� either� the� OUTAUX� switching� frequency� (Register� 0x3F)� or� the�

�PWM� switching� frequency� (Register� 0x40)� is� changed� after� edge� adjustment,� the� synchronization�

�between� OUTAUX� and� the� PWM� edges� is� no� longer� maintained.� The� OUTAUX� delay� must� be�

�adjusted again to synchronize the edges to the PWM edges for the new set of switching frequencies.�

�Table� 92.� Register� 0x5C—OUTAUX� Falling� Edge� Setting� (OUTAUX� Pin)�

�Bits�

�[7:4]�

�Bit� Name�

�t� 14�

�R/W�

�R/W�

�Description�

�These� bits� contain� the� four� LSBs� of� the� 12-bit� t� 14� time.� This� value� is� always� used� with� the� eight�

�bits� of� Register� 0x5B,� which� contains� the� eight� MSBs� of� the� t� 14� time.� Each� LSB� corresponds� to� 5� ns�

�resolution.� The� entire� switching� period� is� divided� into� 40� ns� time� steps.� If� the� t_rise� and� t_fall� of� a�

�PWM� edge� occur� within� the� same� 40� ns� time� step,� the� PWM� output� is� 0� V.� If� the� t_rise� and� t_fall�

�occur� in� different� 40� ns� time� steps,� the� PWM� output� is� set� to� the� programmed� value.� The� absolute�

�maximum� pulse� width� is� t� PERIOD� ?� 5� ns.� Depending� on� the� switching� frequency� and� the� OUTAUX�

�frequency,� there� is� a� constant� lag/lead� time� between� this� edge� and� the� other� edges� (t� 1� to� t� 12� );� there-�

�fore,� OUTAUX� is� not� synchronized� to� the� other� PWM� outputs� but� can� be� made� synchronous� by�

�adjusting� the� delay� accordingly.� If� either� the� OUTAUX� switching� frequency� (Register� 0x3F)� or� the�

�PWM� switching� frequency� (Register� 0x40)� is� changed� after� edge� adjustment,� the� synchronization�

�between� OUTAUX� and� the� PWM� edges� is� no� longer� maintained.� The� OUTAUX� delay� must� be�

�adjusted again to synchronize the edges to the PWM edges for the new set of switching frequencies.�

�3�

�Modulate� enable�

�R/W�

�1� =� PWM� modulation� acts� on� the� t� 14� edge.�

�0� =� no� PWM� modulation� of� the� t� 14� edge.�

�2�

�t� 14� sign�

�R/W�

�1� =� negative� sign.� Increase� of� PWM� modulation� moves� t� 14� right.�

�0� =� positive� sign.� Increase� of� PWM� modulation� moves� t� 14� left.�

�1�

�Regulate� with�

�OUTAUX�

�R/W�

�1� =� control� loop� PWM� modulation� is� regulated� by� OUTAUX.� When� this� bit� is� set,� the� CS1� blanking�

�signal� is� synchronized� with� OUTAUX.�

�0� =� control� loop� PWM� modulation� is� regulated� by� OUTA,� OUTB,� OUTC,� OUTD,� SR1,� and� SR2�

�(normal� mode).�

�0�

�Reserved�

�R/W�

�Reserved.� Set� this� bit� to� 0� for� normal� operation.�

�Rev.� B� |� Page� 74� of� 92�

�相关PDF资料 |

PDF描述 |

|---|---|

| ADP1111ANZ-12 | IC REG BUCK BST INV 12V .2A 8DIP |

| ADP121-ACBZ12R7 | IC REG LDO 1.2V .15A 4WLCSP |

| ADP122AUJZ-2.9-R7 | IC REG LDO 2.9V .3A 5TSOT |

| ADP124ARHZ-2.85-R7 | IC REG LDO 2.85V .5A 8MSOP |

| ADP130AUJZ-2.5-R7 | IC REG LDO 2.5V .35A TSOT-23-5 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ADP1046ADC1-EVALZ | 功能描述:电源管理IC开发工具 RoHS:否 制造商:Maxim Integrated 产品:Evaluation Kits 类型:Battery Management 工具用于评估:MAX17710GB 输入电压: 输出电压:1.8 V |

| ADP1046AWACPZ-R7 | 功能描述:Power Supply Controller Power Supplies 32-LFCSP-WQ (5x5) 制造商:analog devices inc. 系列:- 包装:剪切带(CT) 零件状态:有效 应用:电源 电压 - 输入:0 V ~ 1.6 V 电压 - 电源:3 V ~ 3.6 V 电流 - 电源:20mA 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:32-WFQFN 裸露焊盘,CSP 供应商器件封装:32-LFCSP-WQ(5x5) 标准包装:1 |

| ADP1046DC1-EVALZ | 功能描述:BOARD EVAL DAUGHTERCARD ADP1046 RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PSoC® 主要目的:电源管理,热管理 嵌入式:- 已用 IC / 零件:- 主要属性:- 次要属性:- 已供物品:板,CD,电源 |

| ADP1047 | 制造商:AD 制造商全称:Analog Devices 功能描述:Digital Power Factor Correction Controller |

| ADP1047-300-EVALZ | 制造商:Analog Devices 功能描述:ANAADP1047-300-EVALZ 300W EVALUATION BOA 制造商:Analog Devices 功能描述:EVAL DIGITAL PFC CONTROLLER 300W 制造商:Analog Devices 功能描述:ADP1047, PFC CNTLR, 300W, EVAL KIT |

发布紧急采购,3分钟左右您将得到回复。