- 您现在的位置:买卖IC网 > PDF目录296802 > PH28F128W18BD60A (INTEL CORP) 8M X 16 FLASH 1.8V PROM, 60 ns, PBGA56 PDF资料下载

参数资料

| 型号: | PH28F128W18BD60A |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | 8M X 16 FLASH 1.8V PROM, 60 ns, PBGA56 |

| 封装: | 9 X 11 MM, 1 MM HEIGHT, LEAD FREE, VFBGA-56 |

| 文件页数: | 5/106页 |

| 文件大小: | 1496K |

| 代理商: | PH28F128W18BD60A |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

Intel

Wireless Flash Memory (W18)

07-Dec-2005

Intel Wireless Flash Memory (W18)

Datasheet

102

Order Number: 290701, Revision: 015

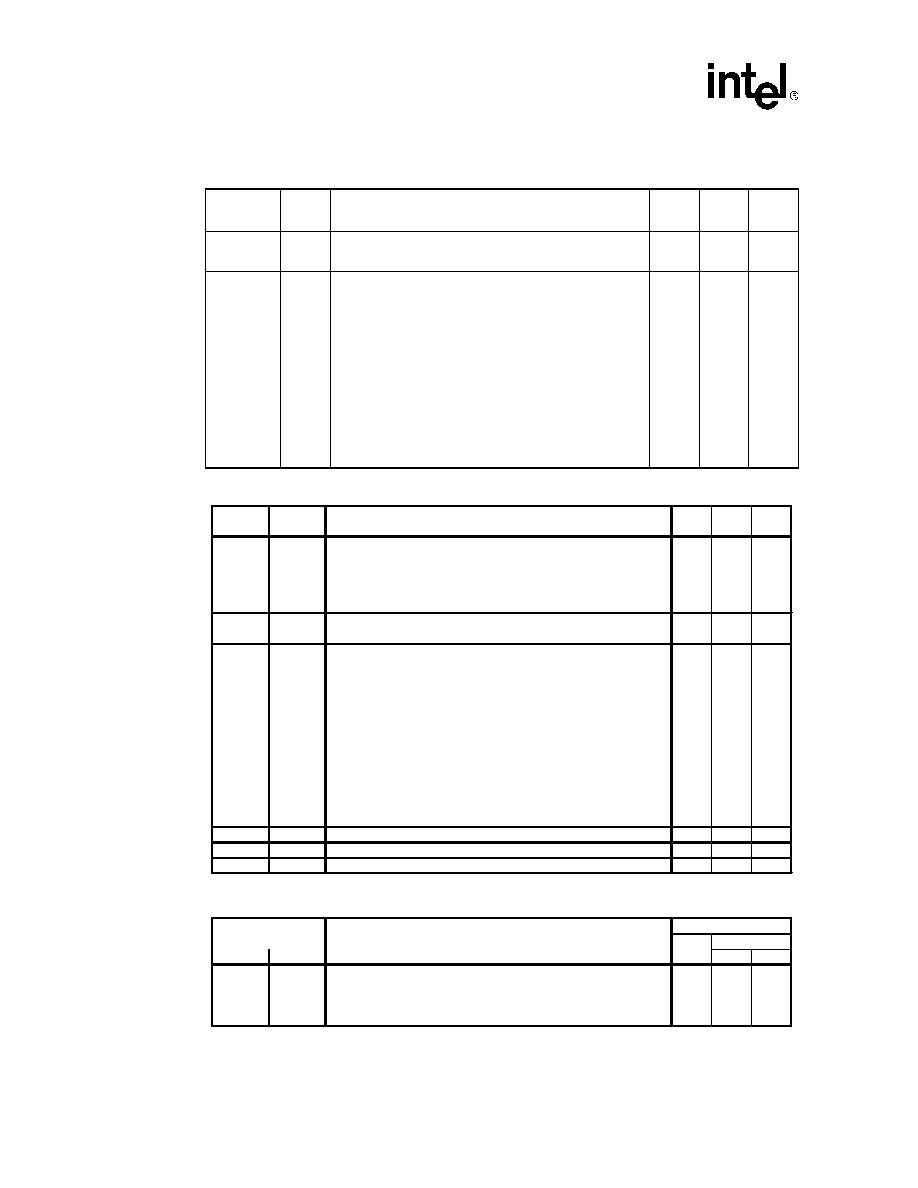

Table 43.

Burst Read Information for Non-muxed Device

Table 44.

Partition and Erase-block Region Information

Table 42.

Protection Register Information

Offset

P = 39h

Lengt

h

Description

(Optional Flash Features and Commands)

Add.

Hex

Code

Value

(P + E)h

1

Number of Protectuib Register fields in JEDEC ID space.

“00h” indicates that 256 protection fields are available.

47:

--01

1

(P + E)h

(P + 10)h

(P + 11)h

(P + 12)h

4

Protection Field 1: Protection Description

This field describes user-available One Time

Programmable (OTP) Protection Register bytes, Some

are pre-programmed with device-unique serial numbers.

Others are user-programmable. Bits are 0-15 point to the

Protection Register lock byte, the section’s first byte. The

following bytes are factory pre-programmed and user-

programmable:

bits 0-7 = Lock/bytes JEDEC-plane physical low address

bites 8-15 = Lock/bytes JEDEC-plane physical high address

bits 16-23 = “n” such that 2n = factory pre-programmed bytes

bits 24-31 = “n” such that 2n = user-programmable bytes

48:

49:

4A:

4B:

--80

--00

--03

80h

00h

8 byte

Offset

(1)

Length

Description

Hex

P = 39h

(Optional flash features and commands)

Add.

Code Value

(P+13)h

1

4C:

--03

8 byte

(P+14)h

1

4D:

--04

4

(P+15)h

1

4E:

--01

4

(P+16)h

1

Synchronous mode read capability configuration 2

4F:

--02

8

(P+17)h

1

Synchronous mode read capability configuration 3

50:

--03

16

(P+18)h

1

Synchronous mode read capability configuration 4

51:

--07

Cont

Page Mode Read capability

bits 0–7 = “n” such that 2

n HEX value represents the number of

read-page bytes. See offset 28h for device word width to

determine page-mode data output width. 00h indicates no

read page buffer.

Number of synchronous mode read configuration fields that

follow. 00h indicates no burst capability.

Synchronous mode read capability configuration 1

Bits 3–7 = Reserved

bits 0–2 “n” such that 2

n+1 HEX value represents the

maximum number of continuous synchronous reads when

the device is configured for its maximum word width. A value

of 07h indicates that the device is capable of continuous

linear bursts that will output data until the internal burst

counter reaches the end of the device’s burstable address

space. This field’s 3-bit value can be written directly to the

Read Configuration Register bits 0–2 if the device is

configured for its maximum word width. See offset 28h for

word width to determine the burst data output width.

Offset

(1)

See table below

P = 39h

Description

Address

Bottom

Top

(Optional flash features and commands)

Len

Bot

Top

(P+19)h

1

52:

Number of device hardware-partition regions within the device.

x = 0: a single hardware partition device (no fields follow).

x specifies the number of device partition regions containing

one or more contiguous erase block regions.

相关PDF资料 |

PDF描述 |

|---|---|

| PHC0683E1133-H | IC SOCKET |

| PHP12NQ15T | N-channel TrenchMOS transistor |

| PHB12NQ15T | N-channel TrenchMOS transistor |

| PHD12NQ15T | N-channel TrenchMOS transistor |

| PHP15N06E | PowerMOS transistor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PH28F160C3BD70A | 制造商:Micron Technology Inc 功能描述:MM#865392FLASH 28F160C3BD 70 VF-PBGA46 C |

| PH28F256L18B85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F256L18B85A | 制造商:Micron Technology Inc 功能描述:MM#875138FLASH 28F256L18B 85 VF-PBGA79 S |

| PH28F256L18T85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F320C3TD70A | 制造商:Micron Technology Inc 功能描述:Flash Mem Parallel 3V/3.3V 32M-Bit 2M x 16 70ns 48-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:MM#869664FLASH 28F320C3TD 70 VF-PBGA47 E |

发布紧急采购,3分钟左右您将得到回复。