- 您现在的位置:买卖IC网 > PDF目录296802 > PH28F128W18BD60A (INTEL CORP) 8M X 16 FLASH 1.8V PROM, 60 ns, PBGA56 PDF资料下载

参数资料

| 型号: | PH28F128W18BD60A |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | 8M X 16 FLASH 1.8V PROM, 60 ns, PBGA56 |

| 封装: | 9 X 11 MM, 1 MM HEIGHT, LEAD FREE, VFBGA-56 |

| 文件页数: | 95/106页 |

| 文件大小: | 1496K |

| 代理商: | PH28F128W18BD60A |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页当前第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

Intel

Wireless Flash Memory (W18)

Datasheet

Intel Wireless Flash Memory (W18)

07-Dec-2005

Order Number: 290701, Revision: 015

89

14.5

Data Hold (RCR[9])

The Data Output Configuration (DOC) bit (RCR[9]) determines whether a data word remains valid

on the data bus for one or two clock cycles. The processor’s minimum data set-up time and the

flash memory’s clock-to-data output delay determine whether one or two clocks are needed.

A DOC set at 1-clock data hold corresponds to a 1-clock data cycle; a DOC set at 2-clock data hold

corresponds to a 2-clock data cycle. The setting of this configuration bit depends on the system and

CPU characteristics. For clarification, see Figure 39, “Data Output Configuration with WAIT

A method for determining this configuration setting is shown below.

To set the device at 1-clock data hold for subsequent reads, the following condition must be

satisfied:

tCHQV (ns) + tDATA (ns) ≤ One CLK Period (ns)

As an example, use a clock frequency of 66 MHz and a clock period of 15 ns. Assume the data

output hold time is one clock. Apply this data to the formula above for the subsequent reads:

11 ns + 4 ns

≤ 15 ns

This equation is satisfied, and data output will be available and valid at every clock period. If tDATA

is long, hold for two cycles.

During page-mode reads, the initial access time can be determined by the formula:

tADD-DELAY (ns) + tDATA (ns) + tAVQV (ns)

Subsequent reads in page mode are defined by:

tAPA (ns) + tDATA (ns)

(minimum time)

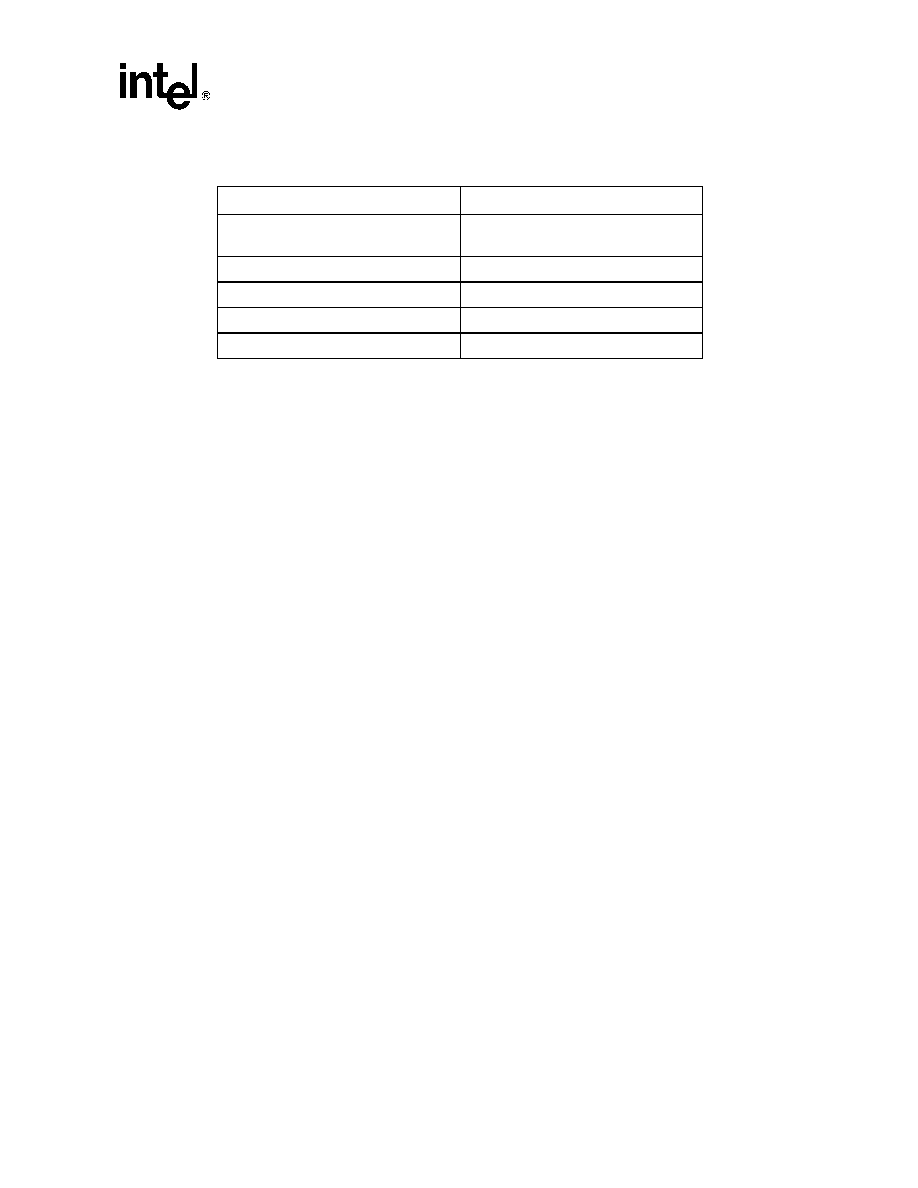

Table 32.

WAIT Signal Conditions

CONDITION

WAIT

CE# = VIH

CE# = VIL

Tri-State

Active

OE#

No-Effect

Synchronous Array Read

Active

Synchronous Non-Array Read

Asserted

All Asynchronous Read and all Write

Asserted

相关PDF资料 |

PDF描述 |

|---|---|

| PHC0683E1133-H | IC SOCKET |

| PHP12NQ15T | N-channel TrenchMOS transistor |

| PHB12NQ15T | N-channel TrenchMOS transistor |

| PHD12NQ15T | N-channel TrenchMOS transistor |

| PHP15N06E | PowerMOS transistor |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PH28F160C3BD70A | 制造商:Micron Technology Inc 功能描述:MM#865392FLASH 28F160C3BD 70 VF-PBGA46 C |

| PH28F256L18B85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F256L18B85A | 制造商:Micron Technology Inc 功能描述:MM#875138FLASH 28F256L18B 85 VF-PBGA79 S |

| PH28F256L18T85 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:StrataFlash Wireless Memory |

| PH28F320C3TD70A | 制造商:Micron Technology Inc 功能描述:Flash Mem Parallel 3V/3.3V 32M-Bit 2M x 16 70ns 48-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:MM#869664FLASH 28F320C3TD 70 VF-PBGA47 E |

发布紧急采购,3分钟左右您将得到回复。