- 您现在的位置:买卖IC网 > PDF目录299522 > MT45W2MW16BBB-856WT 2M X 16 PSEUDO STATIC RAM, 85 ns, PBGA54 PDF资料下载

参数资料

| 型号: | MT45W2MW16BBB-856WT |

| 元件分类: | SRAM |

| 英文描述: | 2M X 16 PSEUDO STATIC RAM, 85 ns, PBGA54 |

| 封装: | 6 X 8 MM, 1 MM HEIGHT, 0.75 MM PITCH, LEAD FREE, VFBGA-54 |

| 文件页数: | 10/56页 |

| 文件大小: | 709K |

| 代理商: | MT45W2MW16BBB-856WT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

4 MEG x 16, 2 MEG x 16

ASYNC/PAGE/BURST CellularRAM MEMORY

09005aef80be1fbd pdf/09005aef80be2036 zip

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Burst CellularRAM_2.fm - Rev. D 9/04 EN

18

2003 Micron Technology, Inc. All rights reserved.

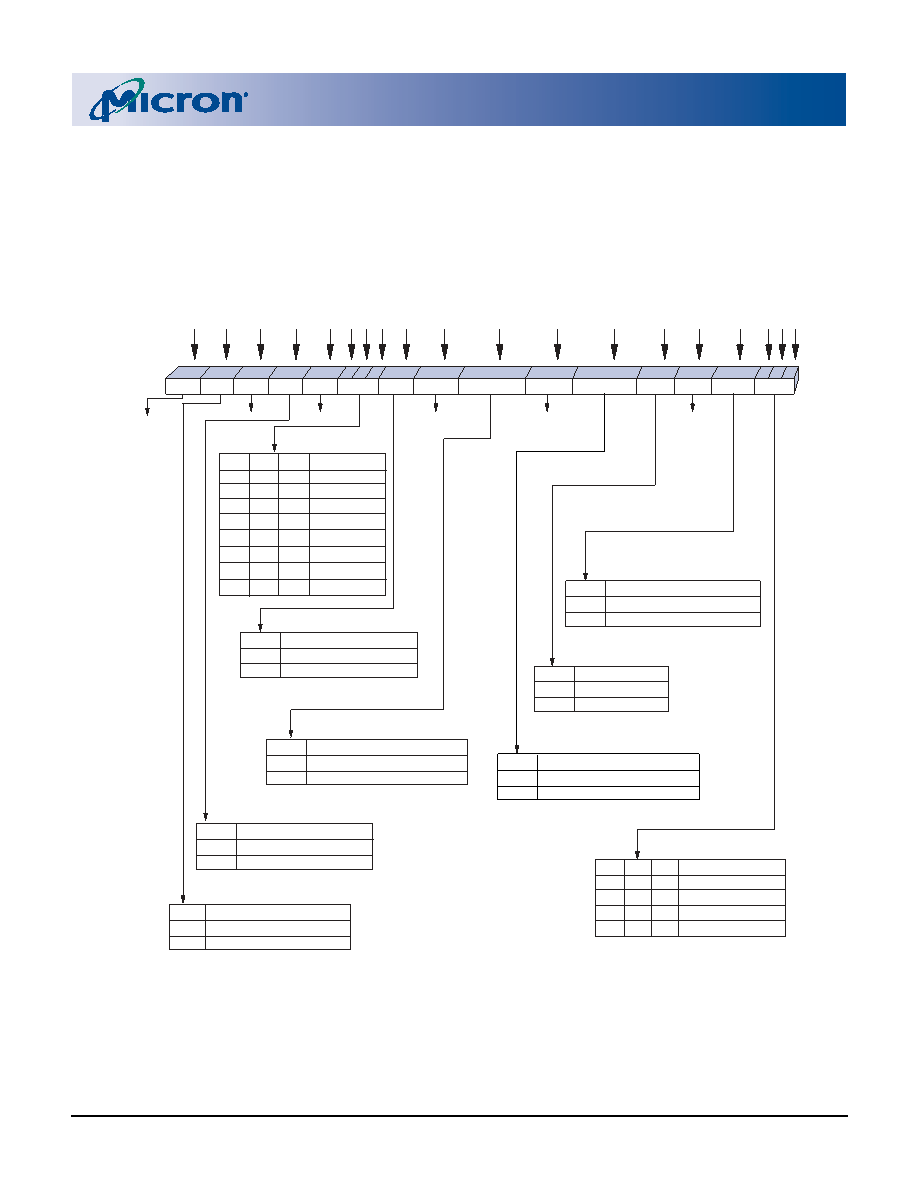

Bus Configuration Register

The BCR defines how the CellularRAM device inter-

acts with the system memory bus. Page mode opera-

tion is enabled by a bit contained in the RCR. Figure 16

describes the control bits in the BCR. At power-up, the

BCR is set to 9D4Fh.

The BCR is accessed using CRE and A[19] HIGH, or

through the configuration register software sequence

with DQ = 0001h on the third cycle.

Figure 16: Bus Configuration Register Definition

NOTE:

1. All burst WRITEs are continuous.

A13

13 12 11

0

Latency

Counter

3

21

WAIT

Polarity

4

5

WAIT

Configuration (WC)

Clock

Configuration (CC)

6

7

8

Output

Impedance

Burst

Wrap (BW)*

14

A12A11 A10

A9

A8

A7

A6

A5

A4

A3

A2 A1 A0

0

1

Operation Mode

Synchronous burst access mode

Asynchronous access mode (default)

BCR[12]

BCR[11]

Latency Counter

BCR[13]

0

1

0

1

0

1

0

1

0

1

0

1

0

1

Code 0–Reserved

Code 1–Reserved

Code 2

Code 3 (Default)

Code 4–Reserved

Code 5–Reserved

Code 6–Reserved

Code 7–Reserved

0

1

WAIT Polarity

Active LOW

Active HIGH (default)

BCR[10]

0

1

WAIT Configuration

Asserted during delay

Asserted one data cycle before delay (default)

0

1

Output Impedance

Full Drive (default)

1/4 Drive

BCR[5]

Burst Wrap (Note 1)

Burst wraps within the burst length

Burst no wrap (default)

BCR[3]

BCR[1] BCR[0]

Burst Length (Note 1)

BCR[2]

15

Burst

Length (BL)*

Reserved

9

10

Reserved

Operating

Mode

Reserved

21–20

A14

A15

A[18:16]

0

1

Register Select

Select RCR

Select BCR

Must be set to "0"

19

18–16

Register

Select

Reserved

A19

A[21:20]

Reserved

Must be set to "0"

All must be set to "0"

BCR[8]

0

1

Clock Configuration

Not supported

Rising edge (default)

BCR[6]

BCR[15]

BCR[19]

0

1

0

1

0

1

0

1

4 words

8 words

16 words

Continuous burst (default)

相关PDF资料 |

PDF描述 |

|---|---|

| MT46H32M32LGCM-5IT:A | 32M X 32 DDR DRAM, 5 ns, PBGA90 |

| MT46HC32M16LFCX-75:B | 32M X 16 DDR DRAM, 7.5 ns, PBGA90 |

| MT46HC32M16LGCM-54IT:B | 32M X 16 DDR DRAM, 5.4 ns, PBGA90 |

| MT47H32M16BT-37VL:A | 32M X 16 DDR DRAM, 0.5 ns, PBGA92 |

| MT47H64M16HQ-3IT:G | 64M X 16 DDR DRAM, 0.4 ns, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT45W2MW16BFB-601 WT | 制造商:Micron Technology Inc 功能描述: |

| MT45W2MW16BFB-701 WT | 制造商:Micron Technology Inc 功能描述: |

| MT45W2MW16BFB-706 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS 54VFBGA - Trays |

| MT45W2MW16BFB-708 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS - Trays |

| MT45W2MW16BFB-856 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 85NS 54VFBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。