- 您现在的位置:买卖IC网 > PDF目录299522 > MT45W2MW16BBB-856WT 2M X 16 PSEUDO STATIC RAM, 85 ns, PBGA54 PDF资料下载

参数资料

| 型号: | MT45W2MW16BBB-856WT |

| 元件分类: | SRAM |

| 英文描述: | 2M X 16 PSEUDO STATIC RAM, 85 ns, PBGA54 |

| 封装: | 6 X 8 MM, 1 MM HEIGHT, 0.75 MM PITCH, LEAD FREE, VFBGA-54 |

| 文件页数: | 8/56页 |

| 文件大小: | 709K |

| 代理商: | MT45W2MW16BBB-856WT |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页

4 MEG x 16, 2 MEG x 16

ASYNC/PAGE/BURST CellularRAM MEMORY

09005aef80be1fbd pdf/09005aef80be2036 zip

Micron Technology, Inc., reserves the right to change products or specifications without notice.

Burst CellularRAM_2.fm - Rev. D 9/04 EN

16

2003 Micron Technology, Inc. All rights reserved.

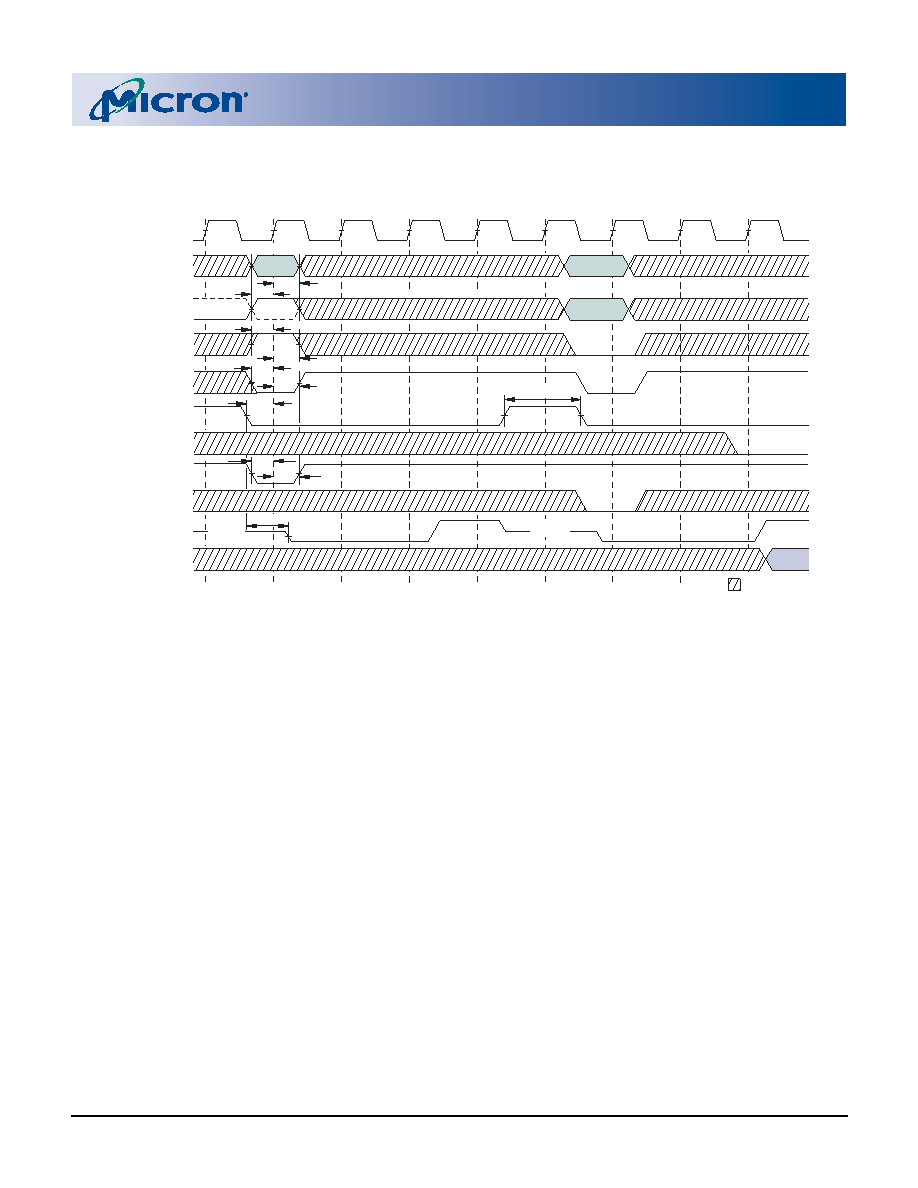

Figure 13: Configuration Register WRITE in Synchronous Mode

Followed by READ ARRAY Operation

NOTE:

1. Non-default BCR settings for configuration register WRITE in synchronous mode followed by READ ARRAY operation:

Latency code two (three clocks); WAIT active LOW; WAIT asserted during delay.

2. A[19] = LOW to load RCR; A[19] = HIGH to load BCR.

3. CE# must remain LOW to complete a burst-of-one WRITE. WAIT must be monitored—additional WAIT cycles caused by

refresh collisions require a corresponding number of additional CE# LOW cycles.

CLK

A[21:0]

(except A19)

A192

CRE

ADV#

CE#

OE#

WE#

LB#/UB#

WAIT

DQ[15:0]

tSP

tHD

tCSP

tSP

tHD

High-Z

DON’T CARE

OPCODE

ADDRESS

High-Z

tCW

Latch Control Register Value

Latch Control Register Address

tCBPH3

DATA

VALID

ADDRESS

相关PDF资料 |

PDF描述 |

|---|---|

| MT46H32M32LGCM-5IT:A | 32M X 32 DDR DRAM, 5 ns, PBGA90 |

| MT46HC32M16LFCX-75:B | 32M X 16 DDR DRAM, 7.5 ns, PBGA90 |

| MT46HC32M16LGCM-54IT:B | 32M X 16 DDR DRAM, 5.4 ns, PBGA90 |

| MT47H32M16BT-37VL:A | 32M X 16 DDR DRAM, 0.5 ns, PBGA92 |

| MT47H64M16HQ-3IT:G | 64M X 16 DDR DRAM, 0.4 ns, PBGA60 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT45W2MW16BFB-601 WT | 制造商:Micron Technology Inc 功能描述: |

| MT45W2MW16BFB-701 WT | 制造商:Micron Technology Inc 功能描述: |

| MT45W2MW16BFB-706 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS 54VFBGA - Trays |

| MT45W2MW16BFB-708 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 70NS - Trays |

| MT45W2MW16BFB-856 WT | 制造商:Micron Technology Inc 功能描述:PSRAM ASYNC 1 32MBIT 2MX16 85NS 54VFBGA - Trays |

发布紧急采购,3分钟左右您将得到回复。