- 您现在的位置:买卖IC网 > PDF目录180051 > M-ORSO82G51BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | M-ORSO82G51BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 112/123页 |

| 文件大小: | 2207K |

| 代理商: | M-ORSO82G51BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页当前第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页

Lattice Semiconductor

ORCA ORSO82G5 Data Sheet

89

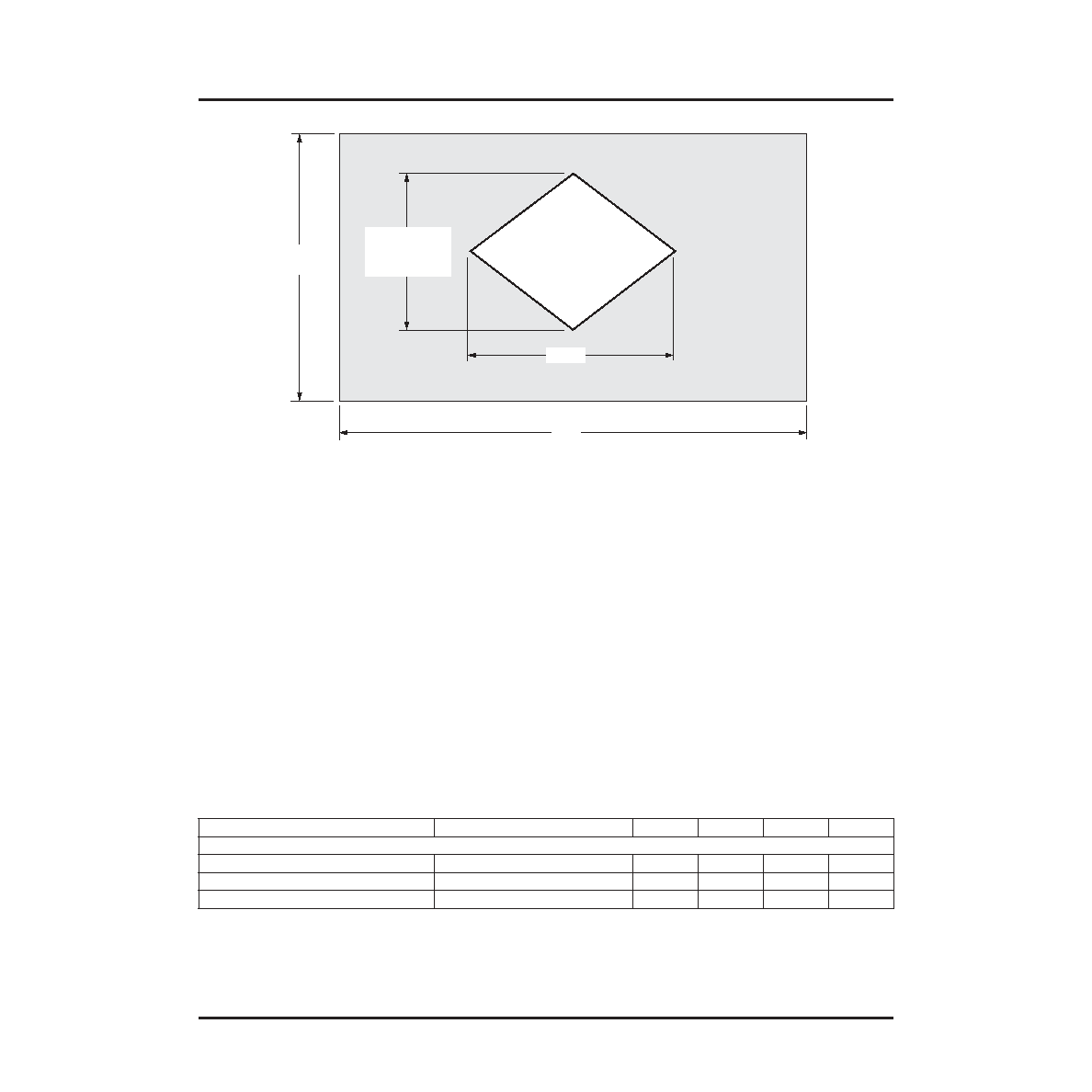

Figure 48. Receive Data Eye-Diagram Template (Differential)

2391(F)

Figure 48 provides a graphical characterization of the SERDES receiver input requirements. It provides guidance

on a number of input parameters, including signal amplitude and rise time limits, noise and jitter limits, and P and N

input skew tolerance. it is believed that incoming data patterns falling within the shaded region of the template will

be received without error (BER < 10E-12), over all specied operating conditions.

Data pattern eye-opening at the receive end of a link is considered the ultimate measure of received signal quality.

Almost all detrimental characteristics of transmit signal and the interconnection link design result in eye-closure.

This combined with the eye-opening limitations of the line receiver can provide a good indication of a links ability to

transfer data error-free.

Signal jitter is of special interest to system designers. It is often the primary limiting characteristic of long digital

links and of systems with high noise level environments. An interesting characteristic of the Clock and Data Recov-

ery (CDR) portion of the ORSO82G5 SERDES receiver is its ability to lter incoming signal jitter that is below the

clock recovery PLL bandwidth (estimated to be about 3 MHz). For signals with high levels of low frequency jitter the

receiver can detect incoming data, error-free, with eye-openings signicantly less than that of Figure 48. This phe-

nomena has been observed in the laboratory.

Eye-diagram measurement and simulation are excellent tools of design. They are both highly recommended when

designing serial link interconnections and evaluating signal integrity.

Table 26. Receiver Specications

Parameter

Conditions

Min

Typ

Max

Unit

Input Data

Stream of Nontransitions

—

72

Bits

Eye Opening Interval

—

0.4

—

UIP-P

Eye Opening Voltage

—

200

—

mVP-P

0.4UI

TBD

1.2 V

UI

PRELIMINAR

Y

相关PDF资料 |

PDF描述 |

|---|---|

| M-ORSO82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G51BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

发布紧急采购,3分钟左右您将得到回复。