- 您现在的位置:买卖IC网 > PDF目录180051 > M-ORSO82G51BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | M-ORSO82G51BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 78/123页 |

| 文件大小: | 2207K |

| 代理商: | M-ORSO82G51BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页当前第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页

Lattice Semiconductor

ORCA ORSO82G5 Data Sheet

58

In the SERDES-only mode the data are simply transferred as 32-bit wide words to and from the FPGA logic. The

next sections describe the signal denitions for the TX and RX paths in the SONET, OPC2 and OPC8 modes. The

signal names unique to an operating mode are preferred for design and are generally the ones used in the

ispLEVER design environment. The labels in the left most column are the hardware FPGA interface names. The

ispLEVER software creates an HDL module with specic names based on the mode selected for each channel.

The interface signals for the embedded RAM are completely independent of these signals. The memory signals are

described in a later section.

Signal Description for TX Path (FPGA to SERDES Core)

Signals are divided across 8 channels with 40 signals per channel. TXDxx[39:0] is the set of 40 signals for a

channel xx.

The data signals multiplexing scheme is similar to the one used for the RXD signals. However, the status signals

multiplexing is different. Please refer to Table 9. for the detailed description of the TXD multiplexing scheme.

For all channels the TXDxx[39:33] signals are not used.

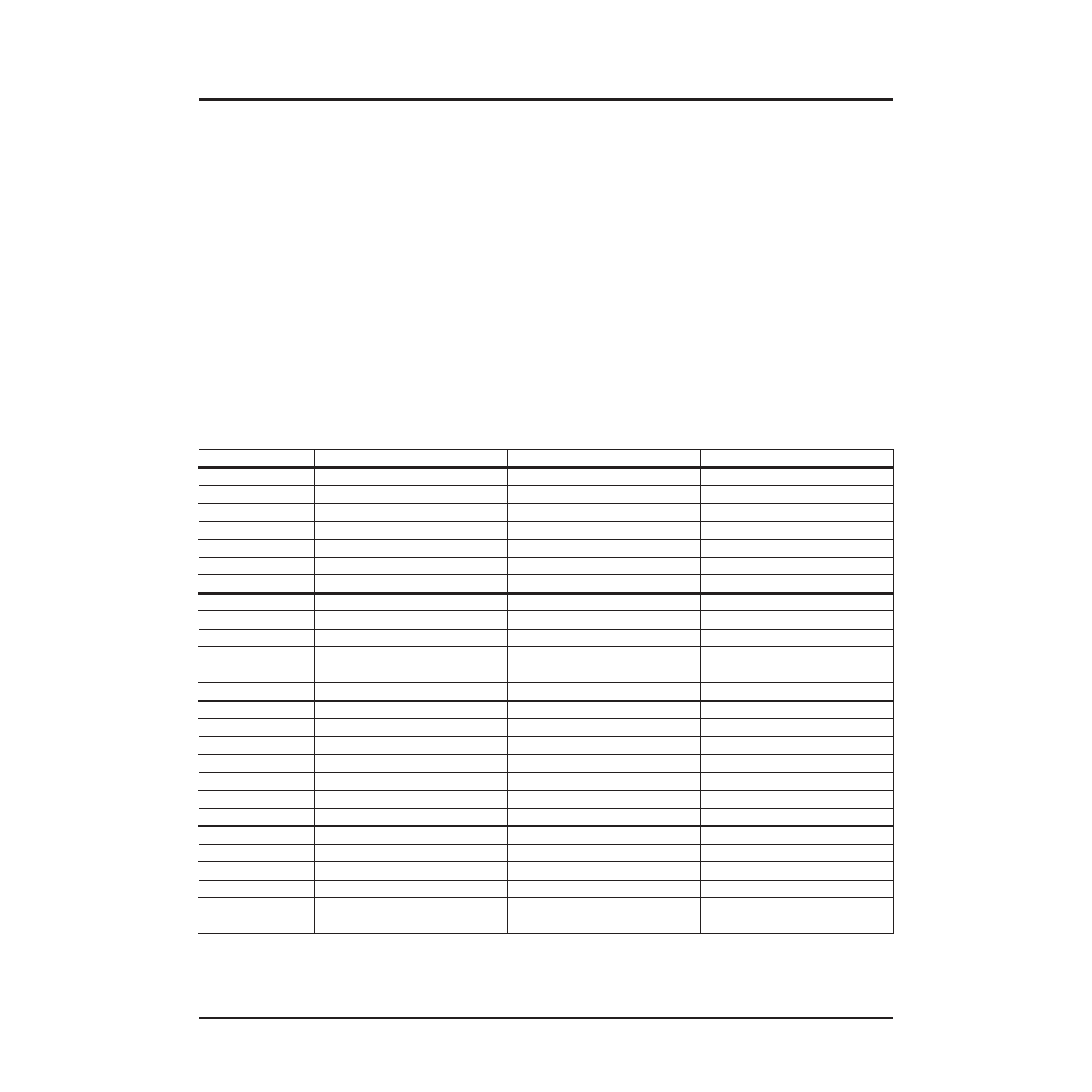

Table 9 summarizes the signals at the FPGA/Core interface in the transmit direction.

Table 9. TX FPGA/Core Interface Signaling

TXDAA

SONET Mode

OPC2 A1 Mode

OPC8 Mode

[39:33]

—

32

DINAA_FP

—

[31:21]

DINAA[31:21]

—

20

DINAA[20]

OPC2_A1_CELLVALID

—

[19:0]

DINAA[19:0]

OPC2_A1[39:20]

OPC8[159:140]

TXDAB

SONET Mode

OPC2 A1 Mode

OPC8 Mode

[39:33]

—

32

DINAB_FP

—

[31:20]

DINAB[31:20]

—

[19:0]

DINAB[19:0]]

OPC2_A1[19:0]]

OPC8[139:120]]

TXDAC

SONET Mode

OPC2 A2 Mode

OPC8 Mode

[39:33]

—

32

DINAC_FP

—

[31:21]

DINAC[31:21]

—

20

DINAC[20]

OPC2_A2_CELLVALID

—

[19:0]

DINAC[19:0]

OPC2_A2[39:20]

OPC8[119:100]

TXDAD

SONET Mode

OPC2 A1 Mode

OPC8 Mode

[39:33]

—

32

DINAD_FP

—

[31:21]

DINAD[31:21]

—

20

DINAD[20]

—

OPC8_CELLVALID

[19:0]

DINAD[19:0]

OPC2_A2[19:0]

OPC8[99:80]

相关PDF资料 |

PDF描述 |

|---|---|

| M-ORSO82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G51BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

发布紧急采购,3分钟左右您将得到回复。