- 您现在的位置:买卖IC网 > PDF目录180051 > M-ORSO82G51BM680-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 1296 CLBS, 333000 GATES, PBGA680 PDF资料下载

参数资料

| 型号: | M-ORSO82G51BM680-DB |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | FPGA |

| 英文描述: | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| 封装: | PLASTIC, FBGA-680 |

| 文件页数: | 92/123页 |

| 文件大小: | 2207K |

| 代理商: | M-ORSO82G51BM680-DB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页当前第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页

Lattice Semiconductor

ORCA ORSO82G5 Data Sheet

70

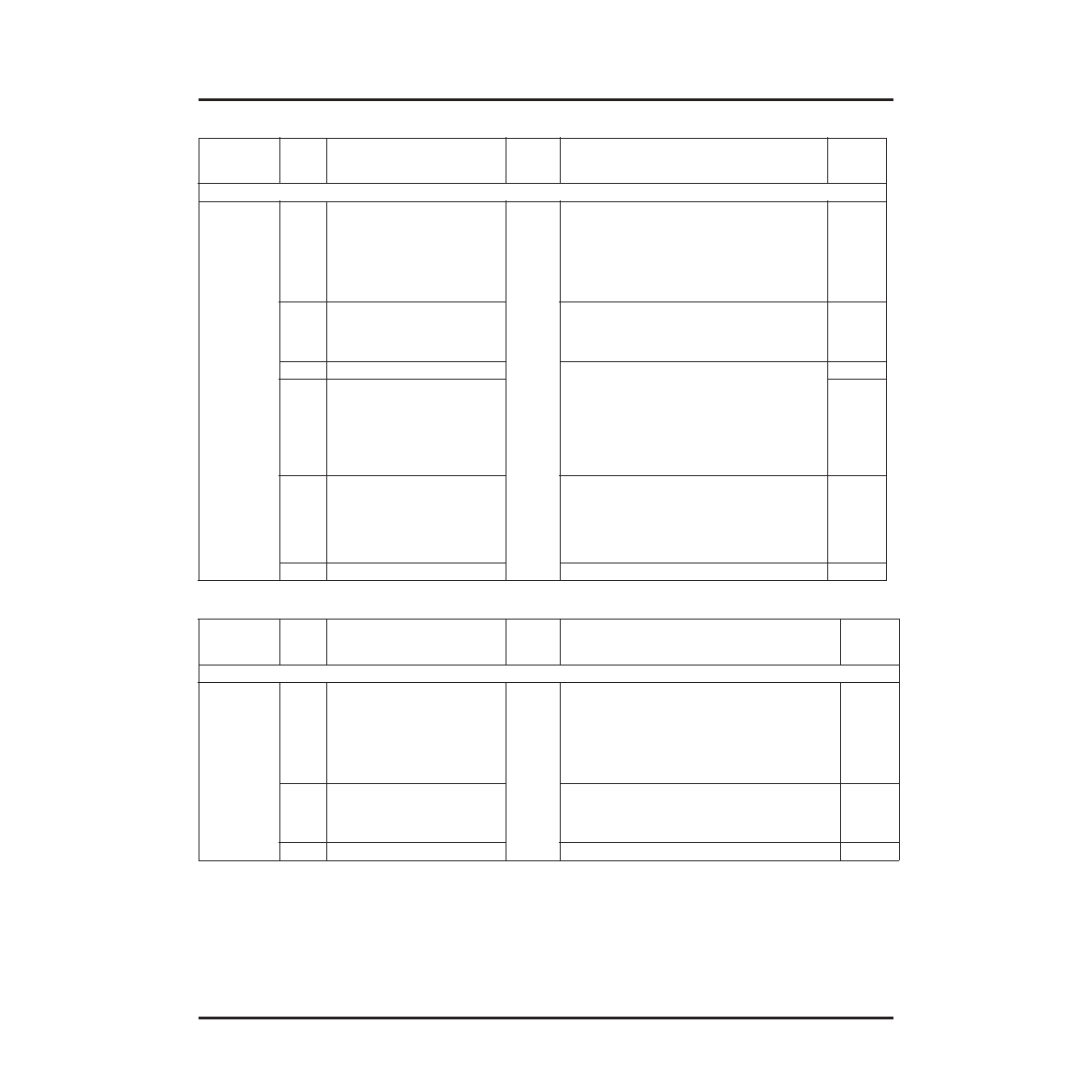

Table 15. SERDES Per-Channel Transmit Conguration Register Descriptions

Table 16. SERDES Per-Channel Receive Conguration Register Descriptions

(0x)

Absolute

Address

Bit

Name

Reset

Value

(0x)

Description

Mode

SERDES Transmit Per-Channel Conguration Registers (Read/Write) xx = [AA, ...,BD]

30002 - AA

30012 - AB

30022 - AC

30032 - AD

30102 - BA

30112 - BB

30122 - BC

30132 - BD

[0]

TXHR_xx

00

Transmit Half Rate Selection Bit, Channel xx.

When TXHR_xx = 1, HDOUT_xx's baud rate =

(REFCLK[A:B]*8) and TCK78[A:B] =(REF-

CLK[A:B]/4); when TXHR_xx=0, HDOUT_xx's

baud rate = (REFCLK[A:B]*16) and

TCK78[A:B]=(REFCLK[A:B]/2).

TXHR_xx = 0 on device reset.

Both

[1]

PWRDNT_xx

Transmit Powerdown Control Bit, Channel xx.

When PWRDNT_xx = 1, sections of the trans-

mit hardware are powered down.

PWRDNT_xx = 0 on device reset.

Both

[2]

PE0_xx

Transmit Preemphasis Selection Bit 0, Channel

xx. PE0_xx and PE1_xx select one of three

preemphasis settings for the transmit section.

PEO_xx=PE1_xx = 0, Preemphasis is 0%

PEO_xx=1, PE1_xx = 0 or PEO_xx=0,

PE1_xx = 1, Preemphasis is 12.5%

PEO_xx=PE1_xx = 1, Preemphasis is 25%.

PEO_xx=PE1_xx = 0 on device reset.

Both

[3]

PE1_xx

Both

[4]

HAMP_xx

Transmit Half Amplitude Selection Bit, Channel

xx. When HAMP_xx = 1, the transmit output

buffer voltage swing is limited to half its normal

amplitude. Otherwise, the transmit output buffer

maintains its full voltage swing.

HAMP_xx = 0 on device reset.

Both

[5:7]

RSVD

Reserved, Always set to "000"

(0x) Abso-

lute

Address

Bit

Name

Reset

Value

(0x)

Description

Mode

SERDES Receive Per-Channel Conguration Registers (Read/Write) xx = [AA, ...,BD]

30003 - AA

30013 - AB

30023 - AC

30033 - AD

30103 - BA

30113 - BB

30123 - BC

30133 - BD

[0]

RXHR_xx

20

Receive Half Rate Selection Bit, Channel xx.

When RXHR_xx =1, HDIN_xx's baud rate =

(REFCLK[A:B]*8) and RCK78[A:B]=(REF-

CLK[A:B]/4); When RXHR_xx=0, HDIN_xx's baud

rate = (REFCLK[A:B]*16) and RCK78[A:B]=(REF-

CLK/2).

RXHR_xx = 0 on device reset.

Both

[1]

PWRDNR_xx

Receiver Power Down Control Bit, Channel xx.

When PWRDNR_xx = 1, sections of the receive

hardware are powered down. PWRDNR_xx = 0

on device reset.

Both

[2:7]

RSVD

Reserved (Bit 2 = 1 on device reset)

相关PDF资料 |

PDF描述 |

|---|---|

| M-ORSO82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G51BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M-ORT82G52BM680-DB | FPGA, 1296 CLBS, 333000 GATES, PBGA680 |

| M.PI-1R1D12 | 1 ELEMENT, 1.1 uH, GENERAL PURPOSE INDUCTOR, SMD |

| M01-014-1452PA | 14 CONTACT(S), MALE, RIGHT ANGLE TELECOM AND DATACOM CONNECTOR, SOLDER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MORTAR-44LB | 制造商:3M Electronic Products Division 功能描述:3M(TM) FIRE BARRIER MORTAR, 44 98040056073 制造商:3M Electronic Products Division 功能描述:Fire Barrier 44 lb Bag |

| MO-RX3930 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS315M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

| MO-RX3930-FS434M | 制造商:未知厂家 制造商全称:未知厂家 功能描述:FSK RECEIVER MODULE |

发布紧急采购,3分钟左右您将得到回复。