参数资料

| 型号: | IP-RIOPHY |

| 厂商: | Altera |

| 文件页数: | 27/212页 |

| 文件大小: | 0K |

| 描述: | IP RAPID I/O |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | 快速输入/输出接口,物理层 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页当前第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页第201页第202页第203页第204页第205页第206页第207页第208页第209页第210页第211页第212页

�� �

�

�

�Chapter� 2:� Getting� Started�

�Qsys� Design� Flow�

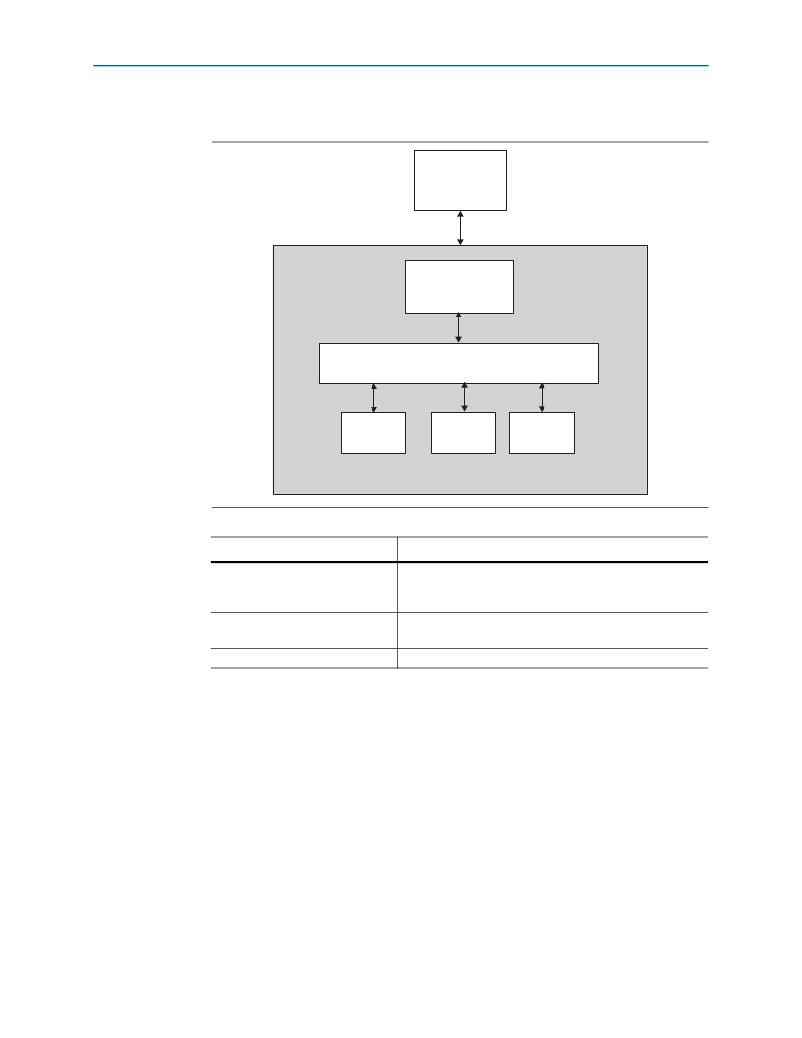

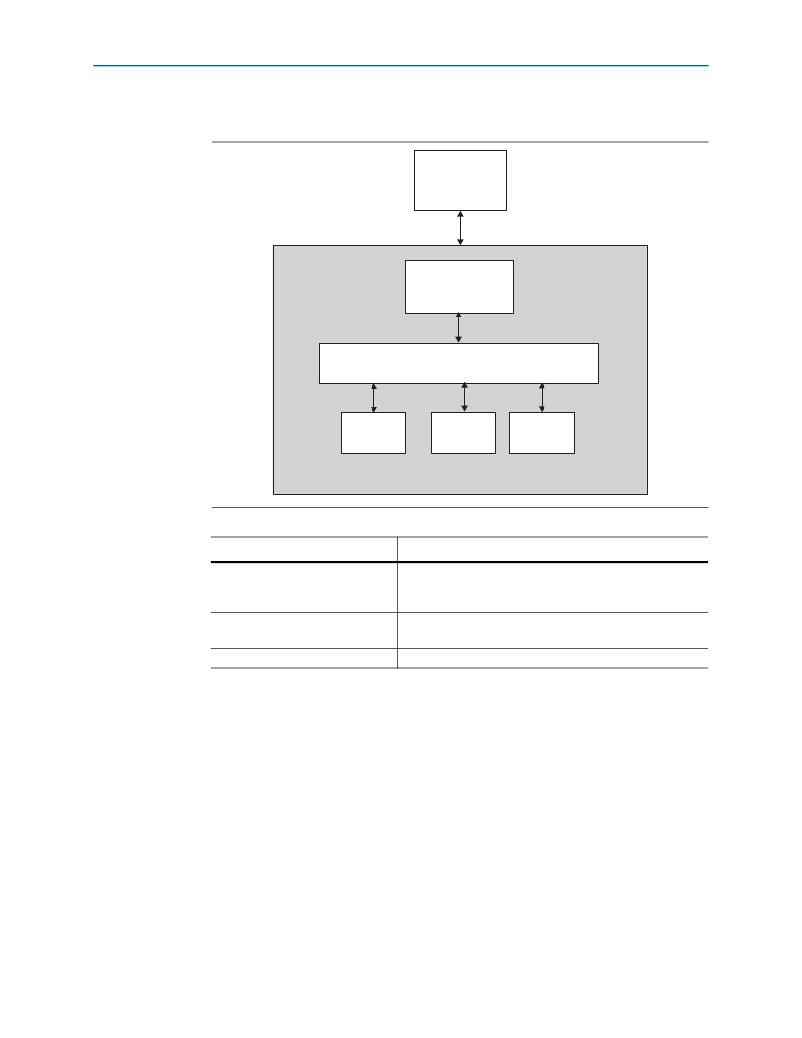

��Figure� 2–2.� Qsys� System�

�RapidIO�

�Simulation�

�Testbench� Module�

�RapidIO�

�MegaCore� Function�

�System� Interconnect�

�2–5�

�DMA�

�On-Chip�

�FIFO�

�Qsys� System�

�On-Chip�

�Memory�

�f�

�For� Information� About�

�System� interconnect�

�Qsys�

�Quartus� II� software�

�Refer� To�

��in� volume� 1� of� the� Quartus� II� Handbook� and� the� Avalon�

��System� Design� with� Qsys� section� in� volume� 1� of� the�

�Quartus� II� Handbook�

�Quartus� II� Help�

�For� information� about� converting� an� SOPC� Builder� system� that� includes� a� RapidIO� IP�

���Specifying� Parameters�

�To� specify� RapidIO� parameters� using� the� Qsys� flow,� follow� these� steps:�

�1.� Create� a� new� Quartus� II� project� using� the� New� Project� Wizard� available� from� the�

�File� menu.�

�2.� On� the� Tools� menu,� click� Qsys� .�

�3.� On� the� System� Contents� tab,� double-click� RapidIO� ,� or� select� RapidIO� and� click�

�Add,� to� add� the� RapidIO� IP� core� to� your� system.� The� RapidIO� parameter� editor�

�appears.�

�May� 2013�

�Altera� Corporation�

�RapidIO� MegaCore� Function�

�User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP-RLDRAMII | IP RLDRAM II CONTROLLER |

| IP-RSDEC | IP REED-SOLOMON DECODER |

| IP-SDI | IP VIDEO INTERFACE - SDI |

| IP-SDRAM/DDR2 | IP DDR2 SDRAM CONTROLLER |

| IP-SLITE2 | IP SERIALLITE II |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPRL2 | 制造商:Carlo Gavazzi 功能描述: |

| IPRL3 | 制造商:Carlo Gavazzi 功能描述: 制造商:Carlo Gavazzi 功能描述:IL FL PB PL 22MM GRN |

| IPRL6 | 制造商:Carlo Gavazzi 功能描述:IL FL PB PL 22MM WHT |

| IP-RLDII/UNI | 功能描述:开发软件 RLDRAM II Controllrs MegaCore RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IP-RLDRAMII | 功能描述:开发软件 RLDRAM II Controllrs MegaCore RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。