- 您现在的位置:买卖IC网 > PDF目录16067 > IPR-POSPHY4 (Altera)IP POS-PHY L4 RENEW PDF资料下载

参数资料

| 型号: | IPR-POSPHY4 |

| 厂商: | Altera |

| 文件页数: | 102/144页 |

| 文件大小: | 0K |

| 描述: | IP POS-PHY L4 RENEW |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | POS-PHY 4 级接口,链路层/物理层 |

| 许可证: | 续用许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页当前第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

�� �

�

�

�6–2�

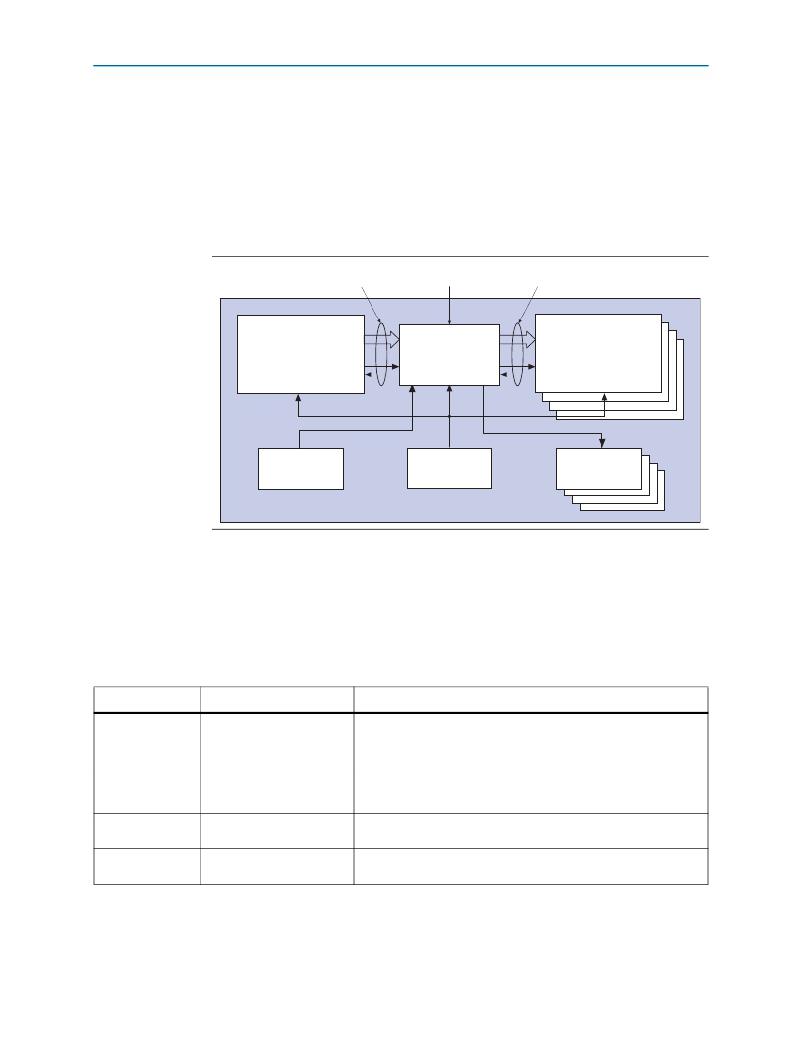

�Chapter� 6:� Testbench�

�Receiver� Testbench� Description�

�The� testbench� consists� of� three� basic� modules:� packet� generation,� user� receiver�

�variation,� and� a� data� analyzer.� All� testbench� modules� are� in� the� <� variation� name� >� _tb.v�

�file.� The� testbench� also� consists� of� multiple� support� modules� for� pin� monitoring,� clock�

�generation,� and� reset� generation� (refer� to� Figure� 6–1� ).� The� packet� generation� module�

�generates� SPI-4.2� packets.� These� packets� are� received� by� the� receiver� MegaCore�

�function,� which� processes� the� packets� and� converts� them� to� Atlantic� interface� format.�

�Finally,� the� data� analyzer� module� receives� the� data� from� the� Atlantic� interface� and�

�verifies� the� correctness� of� the� data� with� an� individual� monitor� for� each� port.�

�Figure� 6–1.� Receiver� Testbench�

�SPI-4.2�

�Interface�

�POS-PHY� Le� v� el� 4�

�Packet� Generation�

�Reset�

�De� v� ice� Under� Test�

�POS-PHY�

�Le� v� el� 4�

�Recei� v� er�

�Variation�

�Clock�

�Generator�

�Atlantic�

�Interface�

�Atlantic� Interface�

�Data� Analyser�

�(one� per� port)�

�Pin� Monitor�

�The� packet� generation� module� begins� by� sending� the� idle� pattern� (� 16'h000f� )� and� then�

�the� training� pattern� (� 16'h0fff� ,� 16'hf000� )� until� the� POS-PHY� Level� 4� receiver�

�MegaCore� function� is� synchronized� to� the� data� source.�

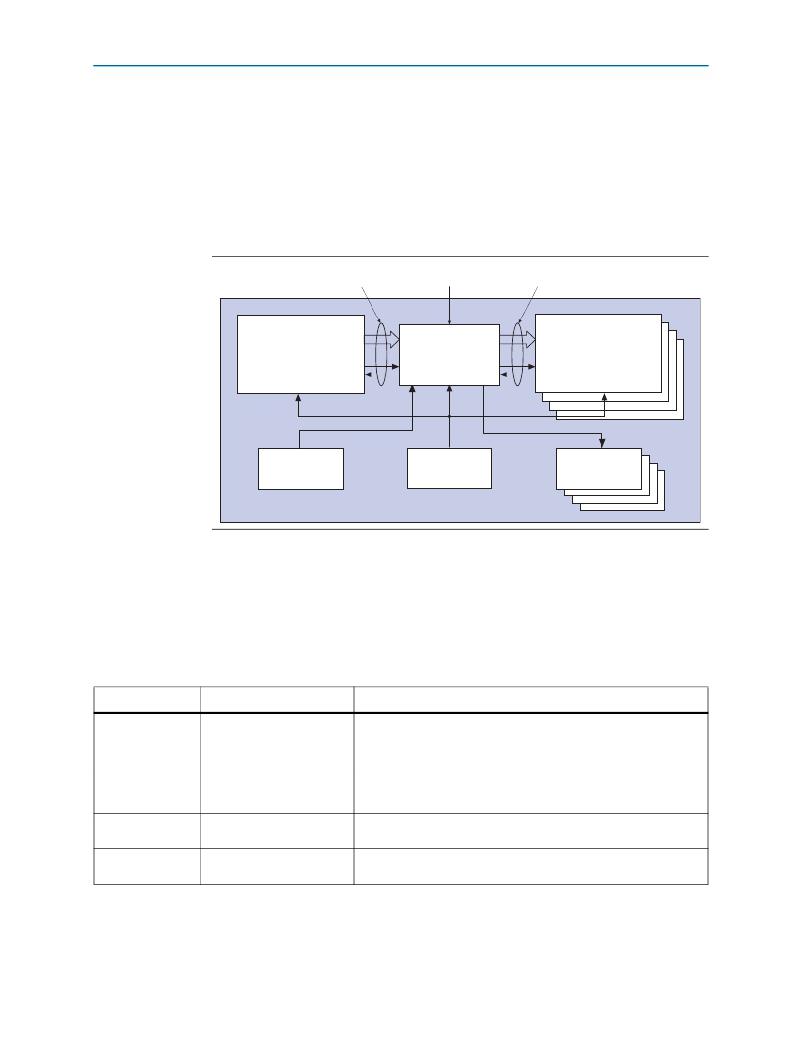

�The� packet� generation� module� then� begins� sending� packets� of� lengths� defined� by� the�

�top-level� testbench.� To� allow� for� automated� packet� checking,� a� special� packet� format�

�is� used.� Table� 6–1� shows� the� format� of� each� packet.�

�Table� 6–1.� Packet� Format�

�Packet� Byte�

�Header� byte�

�Extra� length� byte�

�Number� byte�

�Payload� bytes�

�Format�

�{0,0,len[5:1],ext}�

�{size[16:0]}�

�{N[7:0]� ^� port_num}�

�{N++^� port_num}�

�Description�

�Contains� information� about� the� packet.� len� represents� the� length� of�

�the� packet� if� the� length� can� be� encoded� in� six� bits.� If� the� length� is�

�beyond� 32� bits,� ext� is� set� to� indicate� that� the� next� byte� in� the� packet�

�contains� the� length� information.�

�If� ext� is� 1,� the� extended� expected� packet� size� shows� the� length� of� the�

�packet� including� the� header� (� size� >� 16� bytes)� (optional).�

�Packet� number� (packet� number� begins� at� 'h01� and� is� incremented� by�

�one� for� each� packet)� XOR� ed� with� the� port� number.�

�The� following� bytes� in� the� packet� are� incremented� by� one� and� XOR� ed�

�with� the� port� number.�

�POS-PHY� Level� 4� MegaCore� Function� User� Guide�

�May� 2013� Altera� Corporation�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6337US20D3+T | IC MPU/RESET CIRC 2.00V SOT143-4 |

| M3CWK-3436R | IDC CABLE - MKC34K/MC34M/MPL34K |

| M3AWK-3436R | IDC CABLE - MSC34K/MC34M/MPL34K |

| M3CKK-3436R | IDC CABLE - MKC34K/MC34M/MPK34K |

| M3AKK-3436R | IDC CABLE - MSC34K/MC34M/MPK34K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPR-QDRII/UNI | 功能描述:开发软件 QDRII SRAM Control MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RAPIDIOII | 功能描述:开发软件 RapidIO 1x/2x/4x MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RIOPHY | 功能描述:开发软件 RapidIO MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RLDII/UNI | 功能描述:开发软件 RLDRAM II Controller MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RLDRAMII | 功能描述:开发软件 RLDRAM II Controller MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。