- 您现在的位置:买卖IC网 > PDF目录16067 > IPR-POSPHY4 (Altera)IP POS-PHY L4 RENEW PDF资料下载

参数资料

| 型号: | IPR-POSPHY4 |

| 厂商: | Altera |

| 文件页数: | 97/144页 |

| 文件大小: | 0K |

| 描述: | IP POS-PHY L4 RENEW |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | POS-PHY 4 级接口,链路层/物理层 |

| 许可证: | 续用许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页当前第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

�� �

�

�

�Chapter� 5:� Functional� Description—Transmitter�

�Avalon-MM� Interface� Register� Map�

�5–25�

�1�

�1�

�If� the� hitless� bandwidth� repositioning� (� HBWR� )� register� is� not� enabled,� the� CALM1� ,�

�CALLEN1� ,� CALMEM_DAT� registers� become� reserved.�

�Only� change� the� CALM0� ,� CALLEN0� ,� CALMEM_DAT0� registers� when� the� DISABLED� register� is�

�equal� to� 1,� or� when� the� CALSEL_ACT� register� is� equal� to� 1.� Only� change� the� CALM1� ,�

�CALLEN1� ,� CALMEM_DAT1� registers� when� the� DISABLED� register� is� equal� to� 1,� or� when� the�

�CALSEL_ACT� register� is� equal� to� 0.�

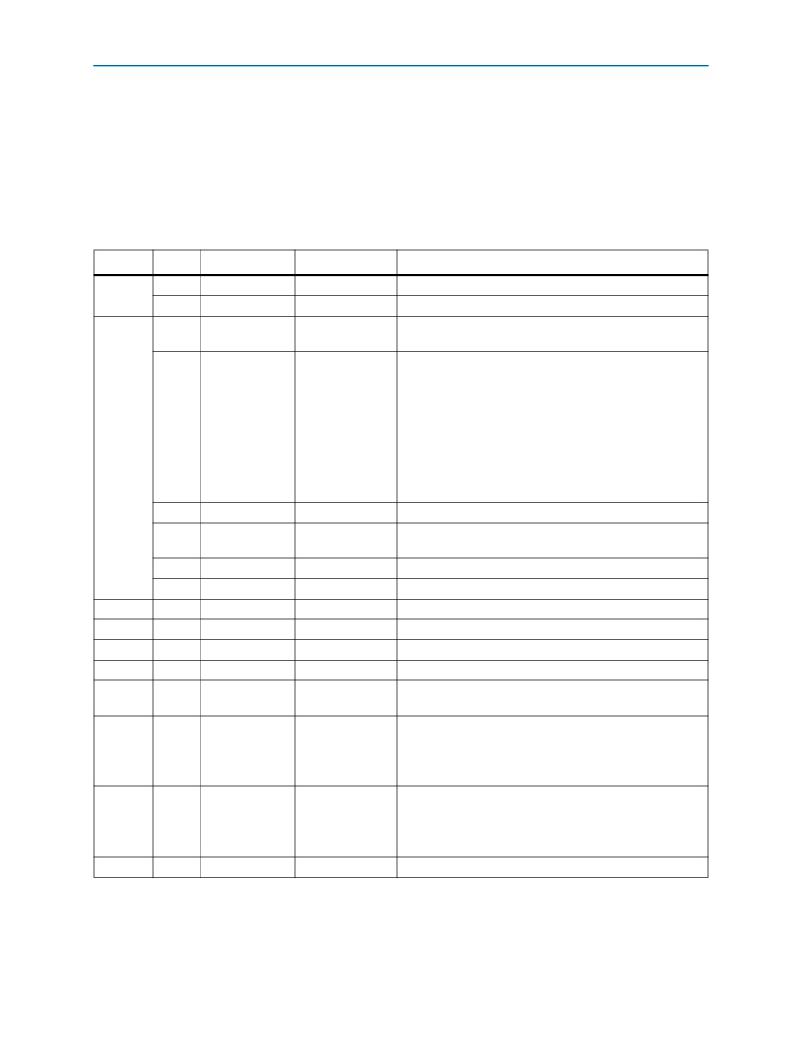

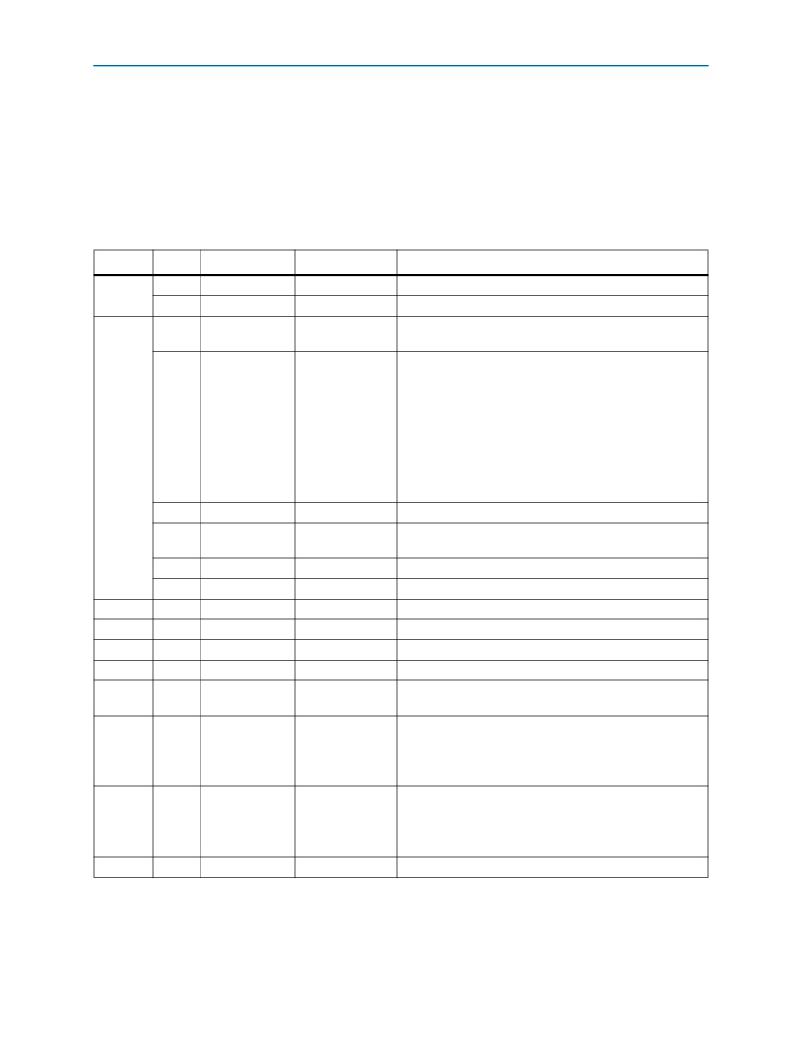

�Table� 5–10.� Avalon-MM� Interface� Register� Map�

�Address�

�0�

�Bits�

�12:0�

�15:13�

�0�

�Name�

�AOT_ID�

�BLOCK_ID�

�HBWR_EN�

�Type�

�Read� only� status�

�Read� only� status�

�Read� write� control�

�Description�

�AOT� code�

�Block� ID�

�HBWR_EN� enables� the� calendar� select� word� in� the� status�

�frame.�

�RSFRM� disables� the� status� finite� state� machine.� This� forces�

�stat_ts_sync� low� and� stat_ts_disabled� high� at� the� end�

�of� the� current� status� frame.� Regular� behavior� eventually�

�resumes� after� this� bit� is� cleared.� The� value� of� the� register� is�

�1�

�1�

�RSFRM�

�Read� write� control�

�OR� ed� with� the� ctl_ts_rsfrm� input.�

�This� bit� resets� to� one.� Therefore,� you� must� reprogram� the�

�calendar� and� clear� this� bit� whenever� the� MegaCore� function� is�

�reset.�

�2�

�3�

�4�

�5�

�RESERVED�

�CALSEL_ACT�

�SYNC�

�DISABLED�

�Reserved�

�Read� only� status�

�Read� only� status�

�Read� only� status�

�Reserved.�

�CALSEL_ACT� is� the� active� calendar� select� word.� 0=� 'b01� ,�

�1=� 'b10�

�Mirror� of� stat_ts_sync� .�

�Mirror� of� stat_ts_disabled� .�

�2�

�3�

�4�

�5�

�6�

�7:0�

�7:0�

�9:0�

�9:0�

�9:0�

�CALM0�

�CALM1�

�CALLEN0�

�CALLEN1�

�CALMEM_ADR�

�Read� write� control�

�Read� write� control�

�Read� write� control�

�Read� write� control�

�Read� write� indirect�

�control�

�CALM� when� CALSEL_ACT� =0.�

�CALM� when� CALSEL_ACT� =1.�

�CALLEN� when� CALSEL_ACT� =0.�

�CALLEN� when� CALSEL_ACT� =1.�

�Refer� to� CALMEM_DAT0� and� CALMEM_DAT1� .�

�If� write,� then� CALMEM_ADR� is� applied� to� the� write� address� of�

�7�

�7:0�

�CALMEM_DAT0�

�Read� write� indirect�

�data�

�RAM� with� CALMEM_DAT0� applied� to� the� write� data.�

�If� read,� then� CALMEM_ADR� is� applied� to� the� read� address� of�

�RAM,� and� resulting� read� data� is� captured� in� CALMEM_DAT0� .�

�If� write,� then� CALMEM_ADR� is� applied� to� the� write� address� of�

�8�

�7:0�

�CALMEM_DAT1�

�Read� write� indirect�

�data�

�RAM� with� CALMEM_DAT1� applied� to� the� write� data.�

�If� read,� then� CALMEM_ADR� is� applied� to� the� read� address� of�

�RAM,� and� resulting� read� data� is� captured� in� CALMEM_DAT1� .�

�9..15�

�—�

�RESERVED�

�Reserved�

�Reserved.�

�May� 2013�

�Altera� Corporation�

�POS-PHY� Level� 4� MegaCore� Function� User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| MAX6337US20D3+T | IC MPU/RESET CIRC 2.00V SOT143-4 |

| M3CWK-3436R | IDC CABLE - MKC34K/MC34M/MPL34K |

| M3AWK-3436R | IDC CABLE - MSC34K/MC34M/MPL34K |

| M3CKK-3436R | IDC CABLE - MKC34K/MC34M/MPK34K |

| M3AKK-3436R | IDC CABLE - MSC34K/MC34M/MPK34K |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPR-QDRII/UNI | 功能描述:开发软件 QDRII SRAM Control MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RAPIDIOII | 功能描述:开发软件 RapidIO 1x/2x/4x MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RIOPHY | 功能描述:开发软件 RapidIO MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RLDII/UNI | 功能描述:开发软件 RLDRAM II Controller MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-RLDRAMII | 功能描述:开发软件 RLDRAM II Controller MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。