- 您现在的位置:买卖IC网 > PDF目录45052 > M66596WG UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 PDF资料下载

参数资料

| 型号: | M66596WG |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA64 |

| 封装: | 0.80 MM PITCH, FBGA-64 |

| 文件页数: | 132/133页 |

| 文件大小: | 1611K |

| 代理商: | M66596WG |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页当前第132页第133页

M66596FP/WG

rev .1.00

2006.3.14

page 96 of 127

3.9.5

Isochronous transfer transmission buffer flush

In the Peripheral mode if a (u) SOF packet is received without an IN token having been received in the interval

frame during isochronous data transmission, the controller operates as a IN token had been corrupted, and clears

the buffer for which transmission is enabled, putting that buffer in the writing enabled state.

If a double buffer is being used at that time and writing has been finished to both buffers, the buffer memory that

was cleared is seen as the data having been sent at the same interval frame, and transmission is enabled for the

other buffer memory.

The timing at which the operation of the buffer flush function begins varies depending on the value set for the

IITV bit.

(1)

If IITV=0

The buffer flush operation starts from the next frame after the pipe becomes valid.

(2)

In any case other than IITV=0

The buffer flush operation is carried out subsequent to the first normal transaction.

Figure 3.27 shows an example of the buffer flush function of the controller. When an unanticipated token prior to

the interval frame is received, the controller sends the written data or a Zero-Length packet are sent in accordance

with buffer state.

Transmission enabled state

Writing in

progress

Buffer A

Buffer B

Writing completed

Empty state

Writing in

progress

Writing completed

Writing in

progress

Writing completed

Transmission enabled state

Figure 3.27 Example of buffer flush function operation

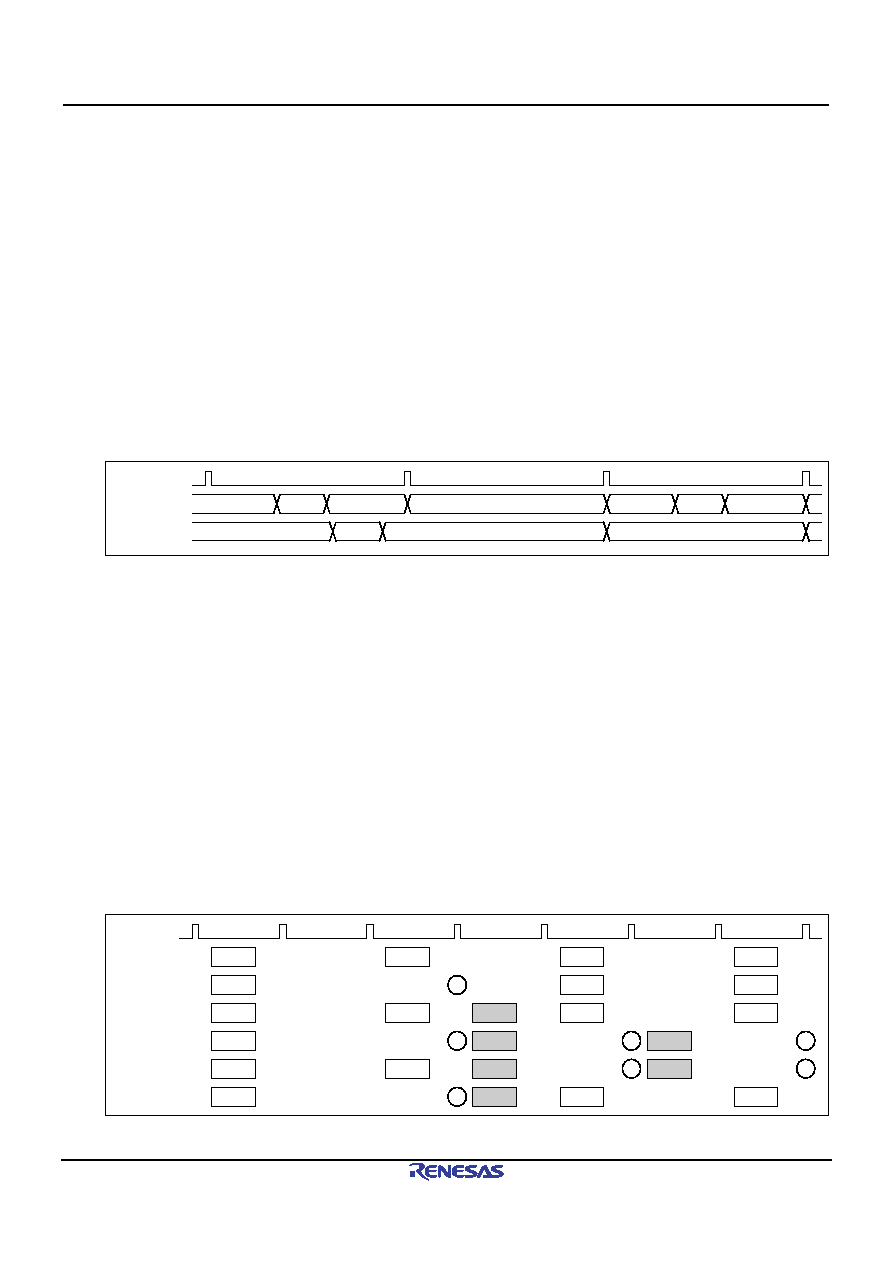

Figure 3.28 shows an example of the controller generating an interval error. There are five types of interval errors,

as noted below. The interval error is generated at the timing indicated by

in the illustration, and the buffer flush

function is activated.

If the interval error occurs during an IN transfer, the buffer flush function is activated, and if it occurs during an

OUT transfer an NRDY interrupt is generated.

The OVRN bit should be used to distinguish between NRDY interrupts such as received packet errors and overrun

errors.

In response to tokens that are shaded in the illustration, responses occur based on the buffer memory status.

(1)

IN direction

(a) If the buffer is in the transmission enabled state, the data is transferred as a normal response .

(b) If the buffer is in the transmission disabled state, a Zero-Length packet is sent and an underrun error

occurs.

(2)

OUT direction

(a) If the buffer is in the reception enabled state, the data is received as a normal response.

(b) If the buffer is in the reception disabled state, the data is decarded and an overrun error occurs.

Token

Normal transfer

Token

Token damaged

Token

Token delayed

Token

Frame misaligned

Token

Packet inserted

Token

1

SOF

Frame misaligned

Figure 3.28 Example of interval error being generated when “IITV=1”

相关PDF资料 |

PDF描述 |

|---|---|

| M6XXLFXI | OTHER CLOCK GENERATOR, QCC16 |

| M300LFXIT | 50 MHz, OTHER CLOCK GENERATOR, QCC16 |

| M74HC00C1R | HC/UH SERIES, QUAD 2-INPUT NAND GATE, PQCC20 |

| M74HC157B1N | HC/UH SERIES, QUAD 2 LINE TO 1 LINE MULTIPLEXER, TRUE OUTPUT, PDIP16 |

| M74HC158C1 | HC/UH SERIES, QUAD 2 LINE TO 1 LINE MULTIPLEXER, INVERTED OUTPUT, PQCC20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M66596WG#RB0Z | 制造商:Renesas Electronics 功能描述:Tray 制造商:Renesas 功能描述:0 |

| M6668 | 制造商:Tamura Corporation of America 功能描述: |

| M66700P | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66700WP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

| M66701P | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:DUAL HIGH-SPEED CCD CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。