- 您现在的位置:买卖IC网 > PDF目录16069 > CORE10/100-RM (Microsemi SoC)IP CORE10/100 ETHERNET MAC PDF资料下载

参数资料

| 型号: | CORE10/100-RM |

| 厂商: | Microsemi SoC |

| 文件页数: | 22/106页 |

| 文件大小: | 0K |

| 描述: | IP CORE10/100 ETHERNET MAC |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页当前第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

�� �

�

�

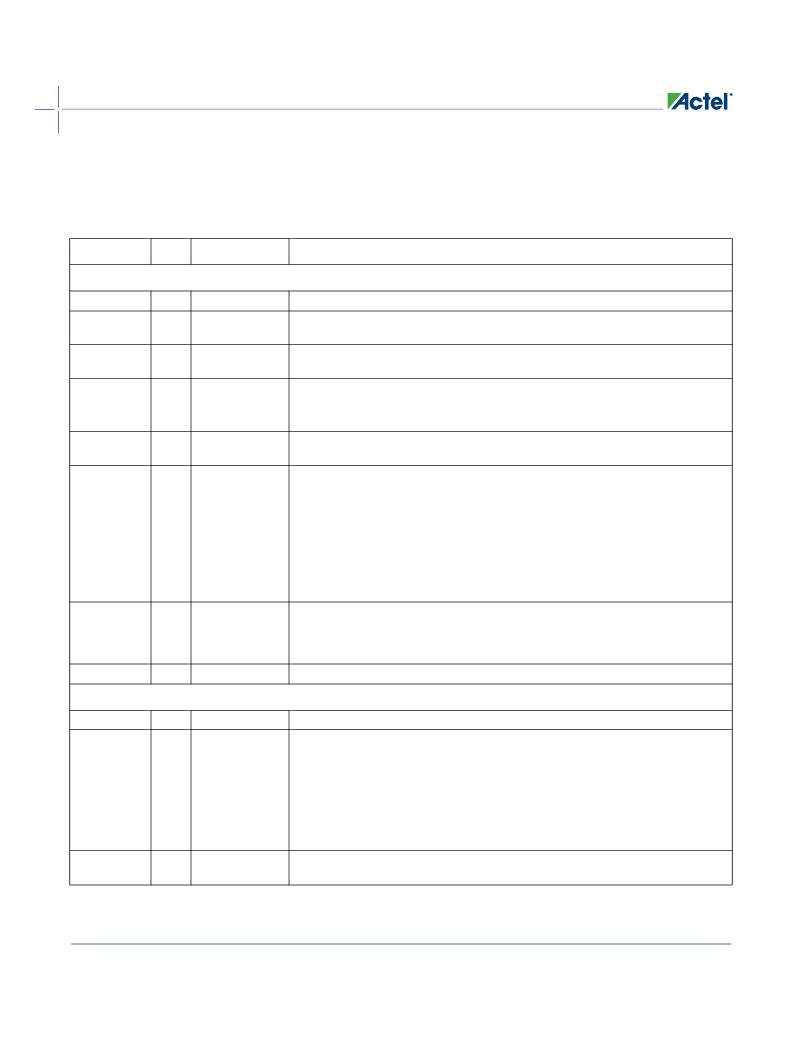

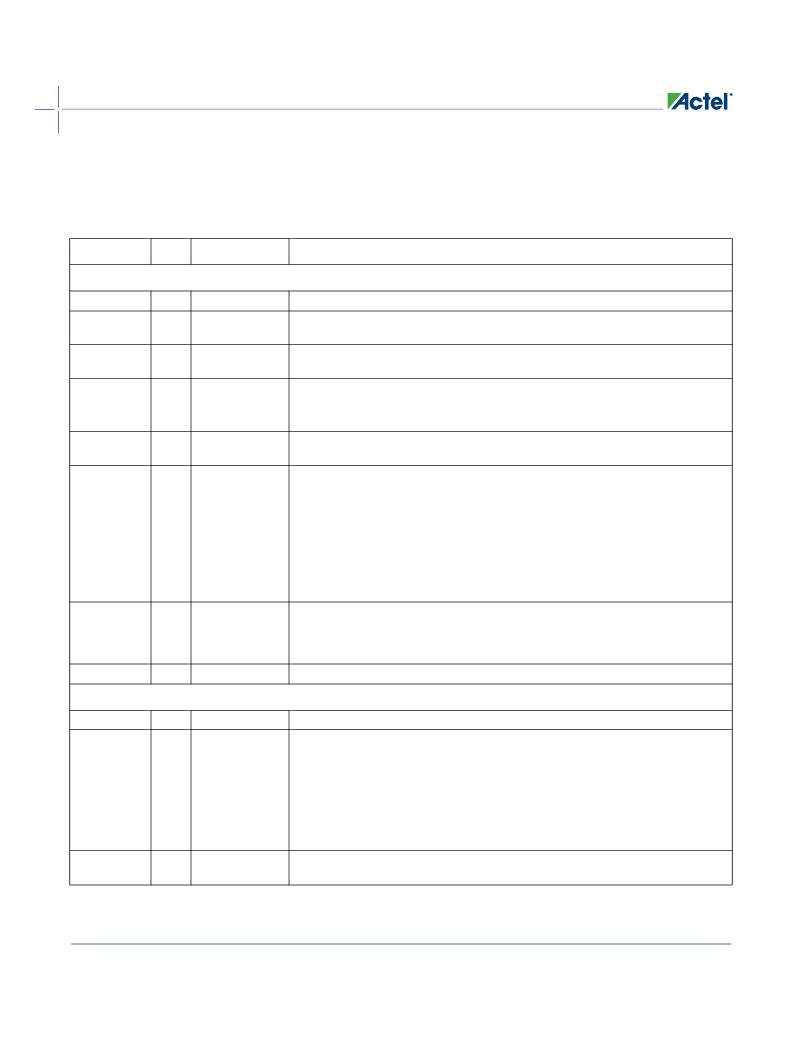

�Interface� Descriptions�

�CSR� Interface� Signals�

��Table� 3-3� ·� Core10100� Signals�

�Core10100� v4.0�

�Name�

�Type�

�Polarity�

�Description�

�Control� and� Status� Register� Interface�

�CLKCSR�

�CSRREQ�

�CSRRW�

�In�

�In�

�In�

�Rise�

�HIGH�

�HIGH�

�CSR� clock�

�This� signal� is� set� by� a� host� to� request� a� data� transfer� on� the� CSR� interface.� It� can� be� a� read� or�

�a� write� request,� depending� on� the� value� of� the� CSRRW� signal.�

�This� signal� indicates� the� type� of� request� on� the� CSR� interface.� Setting� CSRRW� indicates� a�

�read� operation,� and� clearing� it� indicates� a� write� operation.�

�This� signal� is� the� data� byte� enable� to� indicate� which� byte� lanes� of� CSRDATAI� or�

�CSRBE�

�In�

�CSRWIDTH/8�

�CSRDATAO� are� the� valid� data� bytes.� Each� bit� of� the� CSRBE� controls� a� single� byte� lane.�

�All� CSRBE� signal� combinations� are� allowed.�

�CSRDATAI�

�In�

�CSRWIDTH�

�The� write� data� is� provided� by� the� system� on� the� CSRDATAI� inputs� during� the� write�

�request.�

�The� CSRADDR� receives� the� address� of� an� individual� CSR� data� transaction.�

�The� meaning� of� CSRADDR� depends� on� the� CSRWIDTH� parameter.�

�For� CSRWIDTH� =� 32� (32-bit� interface),� only� the� CSRADDR� bits� from� 6� down� to� 2� are�

�CSRADDR�

�In�

�8�

�significant.� The� addresses� are� longword-aligned� (32-bit)� in� this� mode.�

�For� CSRWIDTH� =� 16� (16-bit� interface),� the� CSRADDR� bits� from� 6� down� to� 1� are�

�significant.� The� addresses� are� word-aligned� (16-bit)� in� this� mode.�

�For� CSRWIDTH� =� 8� (8-bit� interface),� all� bits� of� CSRADDR� are� significant.� The� addresses�

�are� byte-aligned� (8-bit)� in� this� mode.�

�The� CSRACK� signal� indicates� either� that� valid� data� is� present� on� the� CSRDATAO� outputs�

�CSRACK�

�Out�

�HIGH�

�during� a� read� request� or� that� the� CSRDATAI� inputs� have� been� sampled� during� a� write�

�request.� The� current� version� of� Core10100� has� the� CSRACK� signal� statically� tied� to� logic�

�1—Core10100� responds� to� reads� and� writes� immediately.�

�CSRDATAO�

�Out�

�CSRWIDTH�

�The� CSRDATAO� signal� provides� the� read� data� in� response� to� a� read� request.�

�Data� Interface�

�CLKDMA�

�In�

�Rise�

�Data� clock�

�The� DATAACK� input� is� an� acknowledge� signal� supplied� by� the� host� in� response� to� the�

�MAC’s� request.� In� the� case� of� a� read� operation,� DATAACK� indicates� valid� data� is� on� the�

�DATAI� input.� The� DATAI� input� must� be� stable� while� DATAACK� is� set.� In� the� case� of� a�

�DATAACK�

�In�

�HIGH�

�write� operation,� setting� DATAACK� indicates� that� the� host� is� ready� to� fetch� the� data�

�supplied� by� Core10100� on� the� DATAO� output.� Regardless� of� the� current� transaction� type�

�(write� or� read),� a� data� transfer� occurs� on� every� rising� edge� of� CLKDMA� on� which� both�

�DATAREQ� and� DATAACK� are� set.� The� DATAACK� signal� can� be� asserted� or�

�deasserted� at� any� clock� cycle,� even� in� the� middle� of� a� burst� transfer.�

�DATAI�

�22�

�In�

�DATAWIDTH�

�The� read� data� must� be� provided� on� the� DATAI� input� by� the� system� in� response� to� a� read�

�request.�

�v4.0�

�相关PDF资料 |

PDF描述 |

|---|---|

| M3CMK-2040K | IDC CABLE - MKC20K/MC20F/MCG20K |

| M3AMK-2040K | IDC CABLE - MSC20K/MC20F/MCG20K |

| M3UUK-4020K | IDC CABLE - MKS40K/MC40F/MKS40K |

| BQ26221PWG4 | IC BATTERY MONITOR HP 8-TSSOP |

| MAX6328UR29+T | IC MPU/RESET CIRC 2.93V SOT23-3 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| CORE10GMAC-OM | 功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1 |

| CORE10GMAC-OMFL | 功能描述:HW/SW/OTHER 制造商:microsemi corporation 系列:* 零件状态:在售 标准包装:1 |

| CORE12X4 | 制造商:Bogen Communications 功能描述:12 X 4 MATRIX CONTROLLER |

| CORE1553BBC-AN | 功能描述:IP MODULE CORE1553 BUS CTLR RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

| CORE1553BBC-AR | 功能描述:IP MODULE CORE1553 BUS CTLR RoHS:否 类别:编程器,开发系统 >> 软件 系列:* 标准包装:1 系列:ISE® 设计套件 类型:订阅 适用于相关产品:Xilinx FPGAs 其它名称:Q4986209T1081384 |

发布紧急采购,3分钟左右您将得到回复。