参数资料

| 型号: | IP-POSPHY4 |

| 厂商: | Altera |

| 文件页数: | 81/144页 |

| 文件大小: | 0K |

| 描述: | IP POS-PHY L4 |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | POS-PHY 4 级接口,链路层/物理层 |

| 许可证: | 初始许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

�� �

�

�

�Chapter� 5:� Functional� Description—Transmitter�

�5–9�

�Clock� Structure�

�Multiple� Clock� Domain�

�In� multiple� clock� domain� mode,� the� tdint_clk� clocks� the� protocol� logic� of� the�

�MegaCore� function,� and� the� read� side� of� the� Atlantic� FIFO� buffers.�

�In� multiple� clock� mode,� an� extra� input� clock� is� instantiated� for� each� Atlantic� FIFO�

�buffer� in� the� MegaCore� function,� which� is� used� for� the� write� side� of� the� buffers.� The�

�naming� convention� for� these� input� clocks� is� aN_atxclk� .� These� clocks� are� inputs� to� the�

�MegaCore� function� and� can� either� be� tied� together� or� controlled� individually.�

�Table� 5–1� shows� the� clock� frequency� values� for� a� data� rate� of� 800� Mbps� on� the� SPI-4.2�

�bus.�

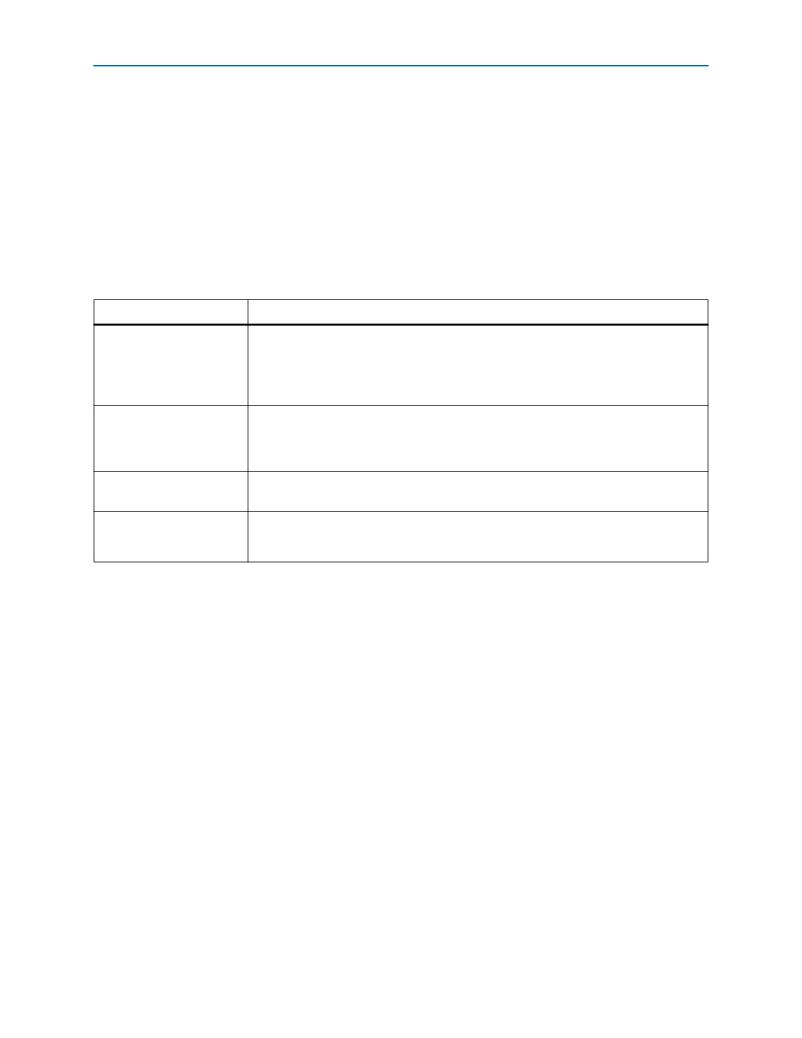

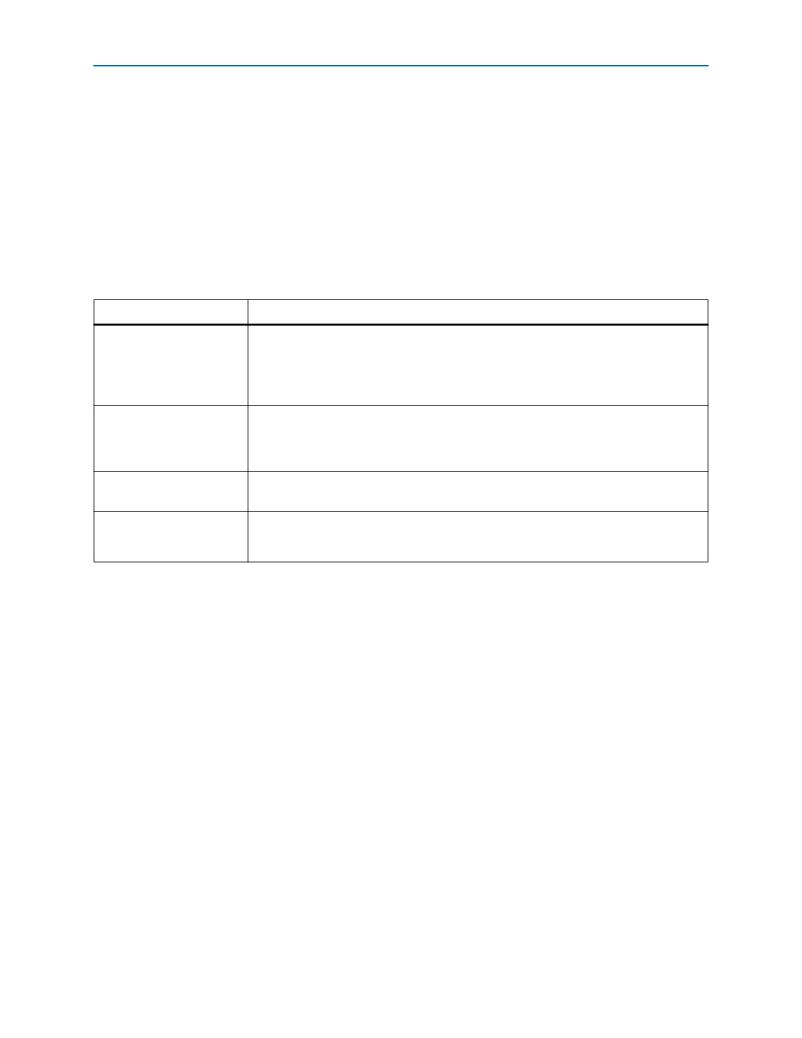

�Table� 5–1.� Clock� Domains�

�Clock� Domain�

�Transmit� MegaCore� function�

�clock� (� trefclk� /� tdint_clk� )�

�Transmit� status� channel�

�clock� (� tsclk� )�

�System� clock� (� txsys_clk� )�

�Transmit� Atlantic� clock�

�(� aN_atxclk� )�

�Description�

�The� trefclk� clock� is� the� input� to� the� MegaCore� function.� The� tdint_clk� clock� is� an� output�

�wire,� and� is� the� output� of� a� fast� PLL.� The� trefclk� can� be� generated� from� multiple� possible�

�sources,� for� various� frequencies.� For� example,� a� SPI-4.2� bus� rate� of� 800� Mbps� requires� a�

�100� MHz� clock� for� a� data� path� width� of� 128� bits,� a� 400� MHz� clock� for� a� data� path� width� of� 32�

�bits,� and� a� 200� MHz� clock� for� a� data� path� width� of� 64� bits.�

�The� SPI-4.2� specification� specifies� a� maximum� status� clock� of� ?� of� the� tdclk� frequency.�

�This� clock� may� be� independent� of� tdclk� .� For� example,� it� is� possible� to� have� a� frequency� of�

�100� MHz� or� less� for� a� data� path� width� of� 128� or� 64� bits,� and� of� 25� MHz� or� less� for� a� data� path�

�width� of� 32� bits.�

�The� txsys_clk� frequency� must� be� faster� than,� or� equal� to,� the� tsclk� frequency.� This� clock�

�transfers� status� to� the� external� status� interface.�

�This� clock� is� typically� asynchronous� to� trefclk� ,� but� this� is� not� a� restriction.� In� the�

�individual� buffers� mode,� there� may� be� as� many� clock� domains� as� there� are� ports,� and� they�

�are� all� allowed� to� be� of� different� phase� and� frequency.�

�May� 2013�

�Altera� Corporation�

�POS-PHY� Level� 4� MegaCore� Function� User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| IP-RIOPHY | IP RAPID I/O |

| IP-RLDRAMII | IP RLDRAM II CONTROLLER |

| IP-RSDEC | IP REED-SOLOMON DECODER |

| IP-SDI | IP VIDEO INTERFACE - SDI |

| IP-SDRAM/DDR2 | IP DDR2 SDRAM CONTROLLER |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPPS054193X | 功能描述:保险丝 800A 1000V 3GKN/75 RoHS:否 制造商:Littelfuse 产品:Surface Mount Fuses 电流额定值:0.5 A 电压额定值:600 V 保险丝类型:Fast Acting 保险丝大小/组:Nano 尺寸:12.1 mm L x 4.5 mm W 安装风格: 端接类型:SMD/SMT 系列:485 |

| IP-QDRII/UNI | 功能描述:开发软件 QDRII SRAM Control MegaCore RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-100GEMAC | 功能描述:开发软件 100G Ethernet Mac MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-100GEMACPHY | 功能描述:开发软件 100 Gb Ethernet MAC PHY MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-100GEPHY | 功能描述:开发软件 100G Ethernet Phy MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

发布紧急采购,3分钟左右您将得到回复。