- 您现在的位置:买卖IC网 > PDF目录69342 > SIS600 (SILICON INTEGRATED SYSTEMS CORP) MULTIFUNCTION PERIPHERAL, PBGA487 PDF资料下载

参数资料

| 型号: | SIS600 |

| 厂商: | SILICON INTEGRATED SYSTEMS CORP |

| 元件分类: | 外设及接口 |

| 英文描述: | MULTIFUNCTION PERIPHERAL, PBGA487 |

| 封装: | BGA-487 |

| 文件页数: | 59/144页 |

| 文件大小: | 1592K |

| 代理商: | SIS600 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页当前第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

SiS600 Pentium II PCI /A.G.P. Chipset

Preliminary V1.0 Jan. 25, 1999

18

Silicon Integrated Systems Corporation

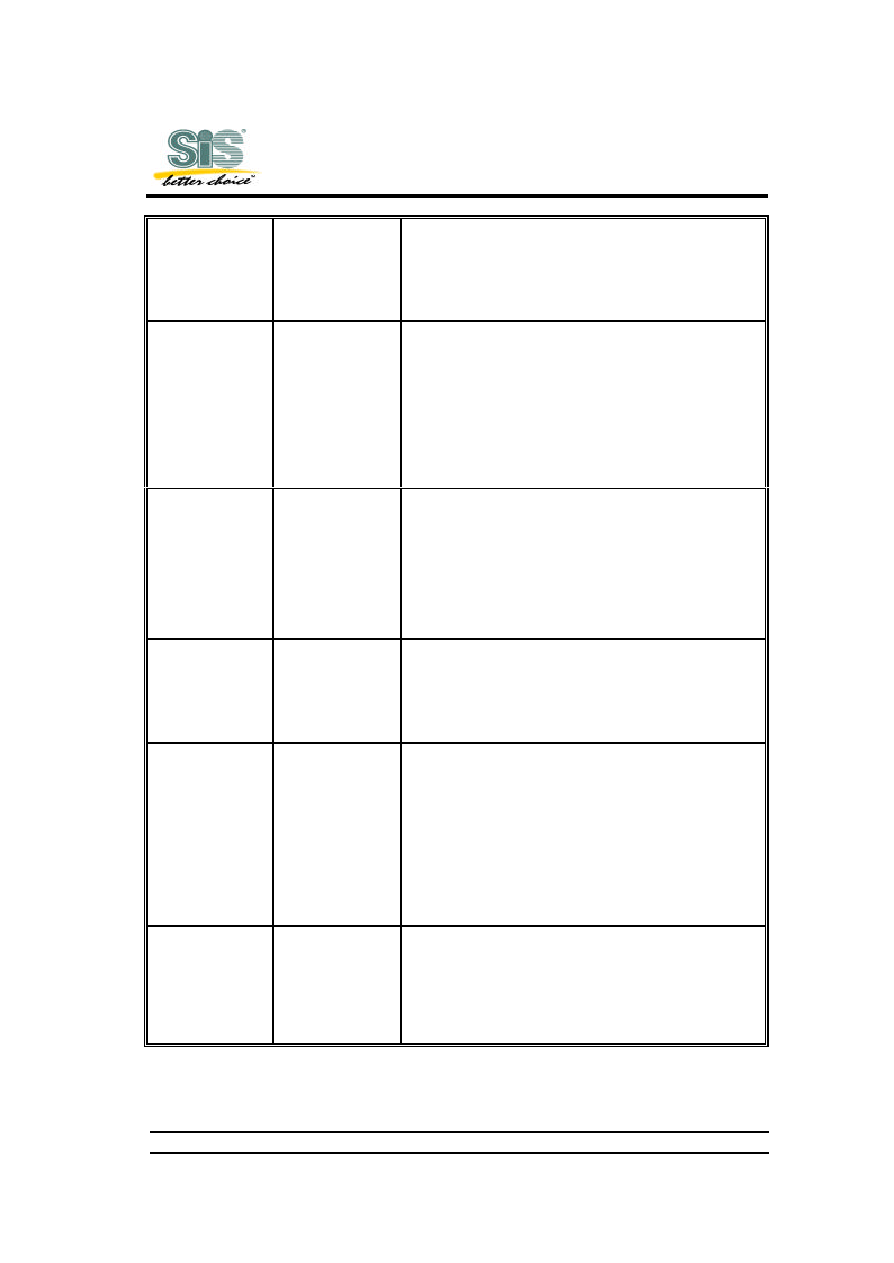

FRAME#

I/O

Frame :

FRAME# is an output when SiS600 is a PCI bus master. SiS600

drives FRAME# to indicate the beginning and duration of an

access.

When SiS600 is a PCI slave, FRAME# is an input

signal.

IRDY#

I/O

Initiator Ready :

IRDY# is an output when SiS600 is a PCI bus master.

The

assertion of IRDY# indicates the current PCI bus master’s ability

to complete the current data phase of the transaction. For a read

cycle, IRDY# indicates that the PCI bus master is prepared to

accept the read data on the following rising edge of the PCI

clock. For a write cycle, IRDY# indicates that the bus master has

driven valid data on the PCI bus. When SiS600 is a PCI slave,

IRDY# is an input.

TRDY#

I/O

Target Ready :

TRDY# is an output when SiS600 is a PCI slave. The assertion

of TRDY# indicates the target agent’s ability to complete the

current data phase of the transaction. For a read cycle, TRDY#

indicates that the target has driven valid data onto the PCI bus.

For a write cycle, TRDY# indicates that the target is prepared to

accept data from the PCI bus. When SiS600 is a PCI master, it is

an input signal.

STOP#

I/O

Stop :

STOP# indicates that the bus master must start terminating its

current PCI bus cycle at the next clock edge and release control

of the PCI bus. STOP# is used for disconnection, retry, and

target-abortion sequences on the PCI bus.

DEVSEL#

I/O

Device Select :

As a PCI target, SiS600 asserts DEVSEL# by doing positive or

subtractive decoding. SiS600 positively asserts DEVSEL# when

the DRAM address is being accessed by a PCI master, PCI

configuration registers or embedded controllers’ registers are

being addressed, or the BIOS memory space is being accessed.

The low 16K I/O space and low 16M memory space are

responded subtractively. The DEVESEL# is an input when

SiS600 is acting as a PCI master. It is asserted by the addressed

agent to claim the current transaction.

PLOCK#

I/O

PCI Lock :

PCI Lock indicates an exclusive bus operation that may require

multiple transactions to complete. When PLOCK# is sampled

asserted at the beginning of a PCI cycle, SiS600 considers itself

a locked resource and remains in the locked state until PLOCK#

is sampled negated on a new PCI cycle.

相关PDF资料 |

PDF描述 |

|---|---|

| SL15100ZC-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL15100ZI-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL18860DCT | 52 MHz, OTHER CLOCK GENERATOR, PDSO10 |

| SL28504RZC | OTHER CLOCK GENERATOR, PDSO64 |

| SL28504RLCT | OTHER CLOCK GENERATOR, QCC64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SIS776DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SIS776DN-T1-GE3 | 制造商:Vishay Siliconix 功能描述:MOSFET N-CH 30V 18.3A 1212-8 |

| SiS778DN-T1-GE3 | 功能描述:MOSFET 30 Volts 35 Amps 52 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

| SIS780DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SiS780DN-T1-GE3 | 功能描述:MOSFET 30 Volts 18 Amps 27.7 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。