- 您现在的位置:买卖IC网 > PDF目录69342 > SIS600 (SILICON INTEGRATED SYSTEMS CORP) MULTIFUNCTION PERIPHERAL, PBGA487 PDF资料下载

参数资料

| 型号: | SIS600 |

| 厂商: | SILICON INTEGRATED SYSTEMS CORP |

| 元件分类: | 外设及接口 |

| 英文描述: | MULTIFUNCTION PERIPHERAL, PBGA487 |

| 封装: | BGA-487 |

| 文件页数: | 91/144页 |

| 文件大小: | 1592K |

| 代理商: | SIS600 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页当前第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

SiS600 Pentium II PCI /A.G.P. Chipset

Preliminary V1.0 Jan. 25, 1999

47

Silicon Integrated Systems Corporation

data from system memory to IDE, the DMA engine will initiate PCI burst cycles to read data from memory into

FIFO until FIFO is full. The FIFO will decrease at the rate of the selected Ultra DMA mode as the IDE controller

doing data-out operation. In the best situation, the FIFO should not be empty during data-out operation otherwise

the burst data transfer on IDE will be suspended.

The Ultra-DMA mode can be enabled on a per-device basis and all three timing modes(0-2) are supported by

programming the corresponding configuration registers. For Ultra-DMA operations, the following signal lines

shall change to their new definition when IDACK# is asserted. These signals will revert back to their old

definitions right after IDACK# is de-asserted.

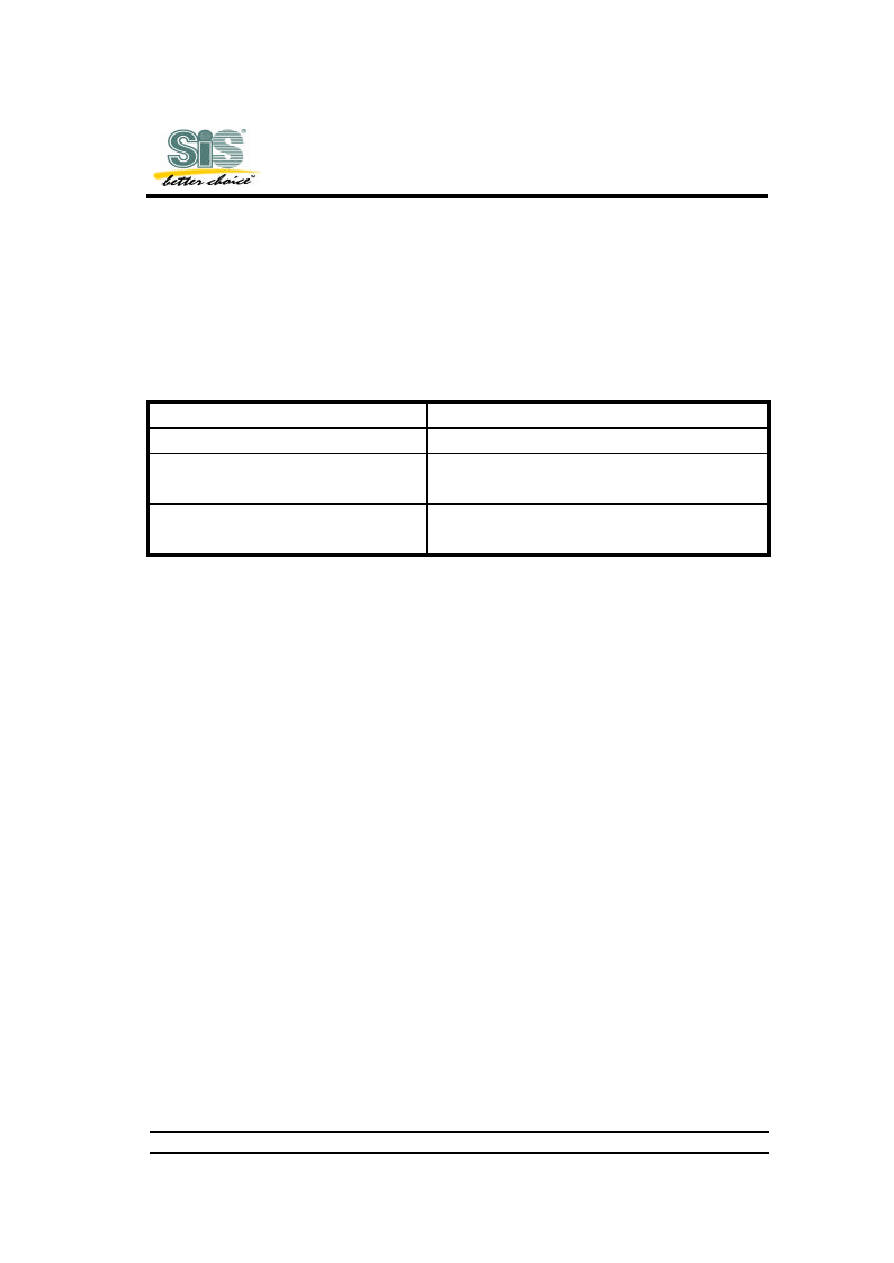

The following table shows the signal line difference between old definition and new definition (Ultra DMA).

Table 5.6-3 Table for Different Command Definition

Old Definition

New Definition

IIOW#

STOP#

IIOR#

HDMARDY# --- data in operation

HSTROBE --- data out operation

ICHRDY#

DSTROBE --- data in operation

DDMARDY# --- data out operation

There are three phases for an Ultra-DMA operation as defined in the protocol: Burst Initiation phase, Data

Transfer phase and Burst Termination phase. The Burst Initiation phase is always initiated by the device when it

asserts IDREQ. The SiS Chip will responds IDACK# after the base address and byte-count in the PRD table entry

is read from system memory. During Data Transfer phase, either the sender or the receiver can pause a burst to

allow for internal data processing and then resume the burst some time later. There are three situations that SiS

Chip will pause a burst:

1.

As a sender during data-out operation and the internal FIFO is empty. The burst will resume after the DMA

engine re-fill the FIFO with data from system memory.

2.

As a receiver during data-in operation and the internal FIFO is full. The burst will resume after the DMA

engine dump the data in FIFO to system memory.

3.

For a PRD table with multiple entries, the DMA engine will start the burst data transfer after base address

and byte-count of one entry are read. When the data transfer for the current entry is completed and the next

entry has not yet been read into the controller, the SiS Chip shall also initiate a pause. After the base address

and byte-count for next entry is read, the burst resumes.

The Burst Termination phase can be initiated by either the SiS Chip or the device. In normal situations, when the

data transfer has reached the byte-count as defined in the last entry of the PRD table, the SiS Chip will initiate a

burst termination by asserting STOP#. After the termination is acknowledged by the device and HSTROBE

signal return to the asserted state, the CRC will be sent on negation of IDACK#. There is an additional situations

that the SiS Chip will also initiate a burst termination:

1.

During the burst data transfer, the host(CPU) is trying to access the command/control block registers. Since

the command/control block access cycle is assigned to have higher priority than data transfer cycles, the SiS

Chip must first terminate the burst, de-asserts the IDACK# signal, generate the corresponding DA[2:0] and

CS[1:0] on IDE bus, and then complete the command/control block register access cycle. After that, the

burst can be resumed by entering the Burst Initiation phase when the device re-asserts IDREQ.

相关PDF资料 |

PDF描述 |

|---|---|

| SL15100ZC-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL15100ZI-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL18860DCT | 52 MHz, OTHER CLOCK GENERATOR, PDSO10 |

| SL28504RZC | OTHER CLOCK GENERATOR, PDSO64 |

| SL28504RLCT | OTHER CLOCK GENERATOR, QCC64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SIS776DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SIS776DN-T1-GE3 | 制造商:Vishay Siliconix 功能描述:MOSFET N-CH 30V 18.3A 1212-8 |

| SiS778DN-T1-GE3 | 功能描述:MOSFET 30 Volts 35 Amps 52 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

| SIS780DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SiS780DN-T1-GE3 | 功能描述:MOSFET 30 Volts 18 Amps 27.7 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。