- 您现在的位置:买卖IC网 > PDF目录69342 > SIS600 (SILICON INTEGRATED SYSTEMS CORP) MULTIFUNCTION PERIPHERAL, PBGA487 PDF资料下载

参数资料

| 型号: | SIS600 |

| 厂商: | SILICON INTEGRATED SYSTEMS CORP |

| 元件分类: | 外设及接口 |

| 英文描述: | MULTIFUNCTION PERIPHERAL, PBGA487 |

| 封装: | BGA-487 |

| 文件页数: | 81/144页 |

| 文件大小: | 1592K |

| 代理商: | SIS600 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页当前第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页

SiS600 Pentium II PCI /A.G.P. Chipset

Preliminary V1.0 Jan. 25, 1999

38

Silicon Integrated Systems Corporation

Fast reset emulation.

Fast A20M# emulation.

CPU involves PCI master arbitration.

Supports CPU idle timer, PCI grant timer and master latency timer.

Supports configuration access format type I, II.

Using configuration mechanism #1.

When CPU issues a line read cycle, converts the toggle mode address to the linear mode address

automatically, then forwards to the PCI side.

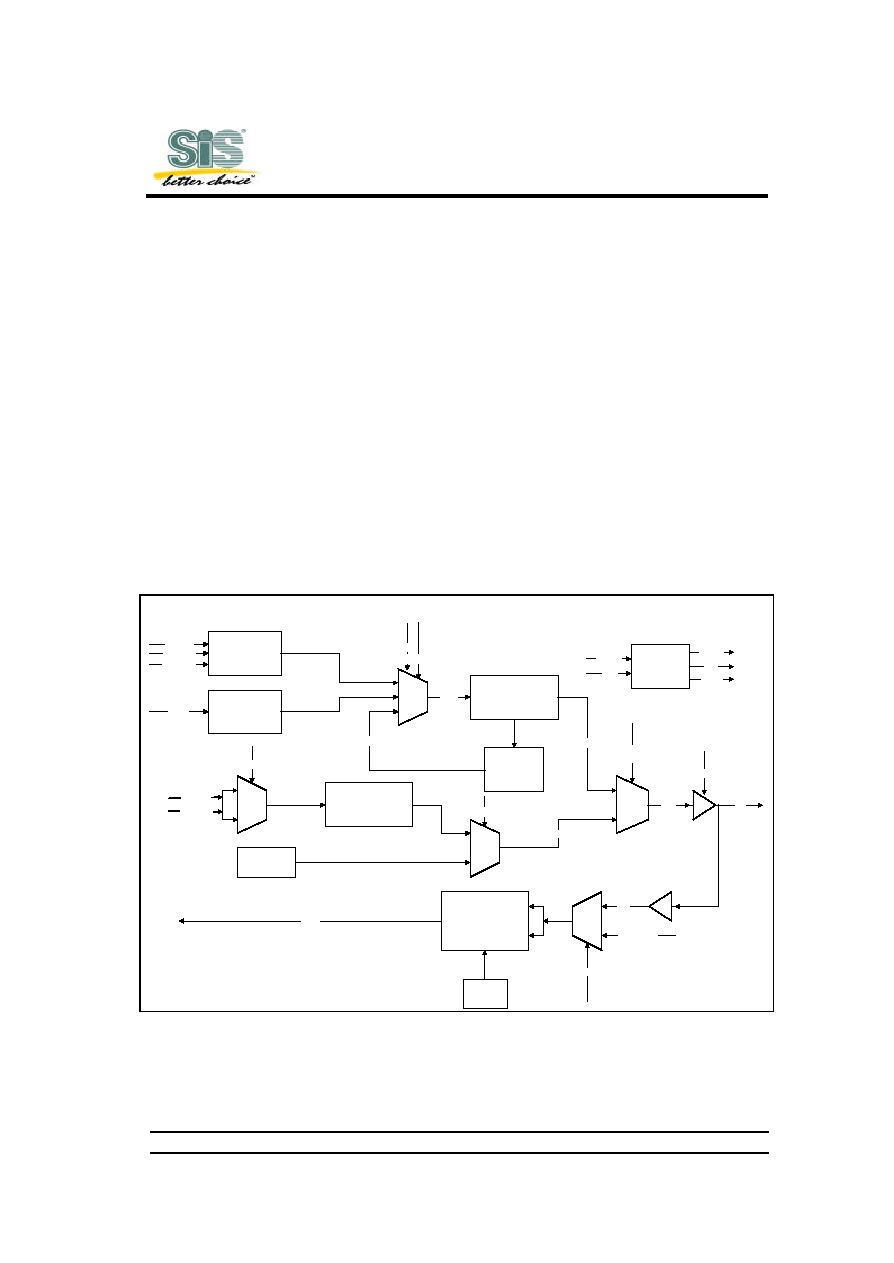

The PCI Master Controller forwards the CPU cycles not targeting the local memory to the PCI bus. In the case of

a 64-bit CPU request or a misaligned 32-bit CPU request the PMR assumes the read assembly and write

disassembly control. A 4 level local posted write buffer is implemented to improve the CPU to PCI memory write

performance. For PCI memory write cycles, the CPU data are pushed into the buffer as soon as FIFO is empty

and then forwarded to PCI bus. If a line read cycle forwarded to the PCI, PCI master controller will convert the

toggle mode address to the linear mode address automatically, then forward to the PCI side. If the consecutive

written data is in DW incremental sequence, they will be transferred to the PCI bus in a burst manner.

The PMR provides a mechanism for converting standard I/O cycles on the CPU bus to Configuration cycles on

the PCI bus.

PCI FORMAT

CONVERTER

CFG ADDRESS

CONVERTER

MUX

ADDR/CMD/ATTR

PING-PONG BUFFER

4level, 3DW

BURST ADDR

GEN &

COMPARE

CFGCYC

NEXT_HA

FADA

MUX

PMR_CMD

0CF8h

REG

PMR_HA

PMR_HD

HGDW

DATA/BEN

PING-PONG BUFFER

4level, 3DW

MUX

HITPIO

Configuration

register

ADA

ADD

MUX

ADOE

AD

ADO

MDATA+PS

L

ADI

MUX

0FFFFFFFFh

Master_abt

PTHFF

4level, 12QW

POINTER

CONTROL

P5HD

RESET &

A20M#

CONTROL

PWRGD

RESET

INIT

PMR BLOCK DIAGRAM

A20M#

HA,

HD,

CMD

PMR_HBE

EXT_AD

PMR_HBE

Figure 5.3-2 Block Diagram for PMR

相关PDF资料 |

PDF描述 |

|---|---|

| SL15100ZC-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL15100ZI-XXX | 200 MHz, OTHER CLOCK GENERATOR, PDSO8 |

| SL18860DCT | 52 MHz, OTHER CLOCK GENERATOR, PDSO10 |

| SL28504RZC | OTHER CLOCK GENERATOR, PDSO64 |

| SL28504RLCT | OTHER CLOCK GENERATOR, QCC64 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SIS776DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SIS776DN-T1-GE3 | 制造商:Vishay Siliconix 功能描述:MOSFET N-CH 30V 18.3A 1212-8 |

| SiS778DN-T1-GE3 | 功能描述:MOSFET 30 Volts 35 Amps 52 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

| SIS780DN | 制造商:VISHAY 制造商全称:Vishay Siliconix 功能描述:N-Channel 30 V (D-S) MOSFET with Schottky Diode |

| SiS780DN-T1-GE3 | 功能描述:MOSFET 30 Volts 18 Amps 27.7 Watts RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。