- 您现在的位置:买卖IC网 > PDF目录16076 > IPR-SLITE2 (Altera)IP SERIALLITE II RENEW PDF资料下载

参数资料

| 型号: | IPR-SLITE2 |

| 厂商: | Altera |

| 文件页数: | 46/110页 |

| 文件大小: | 0K |

| 描述: | IP SERIALLITE II RENEW |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | SerialLite II 协议 |

| 许可证: | 续用许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

�� �

�

�

�Chapter� 3:� Parameter� Settings�

�3–23�

�Link� Layer� Configuration�

�The� threshold� levels� on� both� the� transmitter� and� receiver� Atlantic� FIFO� buffers� differ�

�according� to� implementation.� They� may� depend� on� the� data� traffic,� the� FIFO� depth,�

�and� the� clock� frequencies� for� read� and� write.� Based� on� your� design,� you� can� gauge� the�

�usual� fill� level� of� the� FIFO� buffers� and� determine� the� appropriate� threshold� levels.�

�Data� Integrity� Protection:� CRC�

�If� you� need� error� protection,� you� may� add� CRC� checking� to� your� packet.� The� CRC� is�

�automatically� generated� in� transmission� and� is� automatically� checked� on� reception.�

�On� the� data� port,� a� CRC� check� failure� results� in� the� packet� being� marked� as� bad� using�

�the� rxrdp_err/rxhpp_err� signal� on� the� Atlantic� interface.� You� decide� independently�

�for� each� port� whether� CRC� usage� is� enabled.�

�16-Bit� Versus� 32-Bit� CRC�

�The� SerialLite� II� MegaCore� function� supports� both� 16-bit� and� 32-bit� CRC� algorithms.�

�You� decide� which� CRC� algorithm� to� use� independently� for� each� port.� The� 16-bit�

�algorithm� generates� a� two-byte� result,� and� uses� the� following� polynomial� equation:�

�G(x)� =� X� 16� +� X� 12� +� X� 5� +� 1�

�The� 32-bit� algorithm� generates� a� four-byte� result,� and� uses� the� following� polynomial�

�equation:�

�G(x)� =� X� 32� +� X� 26� +� X� 23� +� X� 22� +� X� 16� +� X� 12� +� X� 11� +� X� 10� +� X� 8� +� X� 7� +� X� 5� +� X� 4� +� X� 2� +� X� +� 1�

�The� 16-bit� version� provides� excellent� protection� for� packets� smaller� than� about� 1�

�KBytes.� For� larger� packets,� CRC-32� can� be� considered,� but� it� requires� significantly�

�more� logic,� especially� in� implementations� requiring� many� lanes.� At� 16� lanes,� CRC-32�

�logic� may� constitute� as� much� as� half� of� the� logic� of� the� entire� SerialLite� II� instantiation.�

�Therefore,� CRC-32� should� only� be� used� when� absolutely� necessary.�

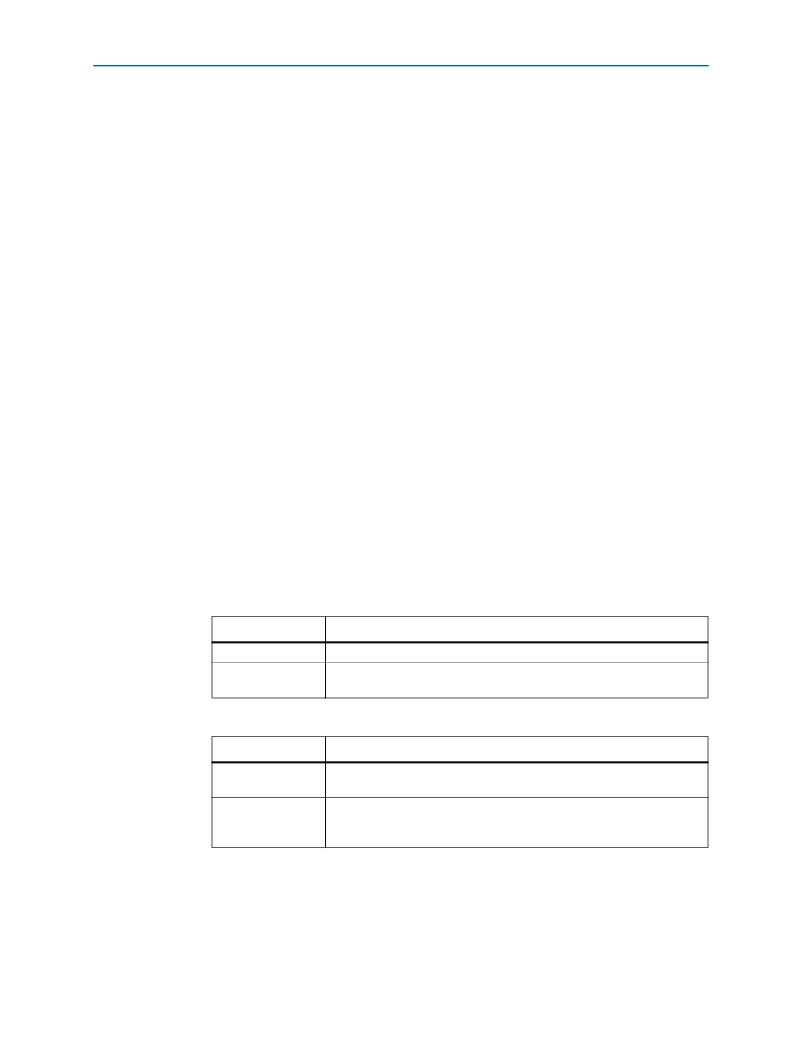

��Table� 3–8.� CRC� Options�

�Option�

�Enabled�

�Disabled�

�Description�

�CRC� logic� is� created.� CRC� usage� is� specified� independently� for� each� port.�

�CRC� logic� is� not� created.� CRC� usage� is� specified� independently� for� each�

�port.� This� is� the� default� CRC� setting.�

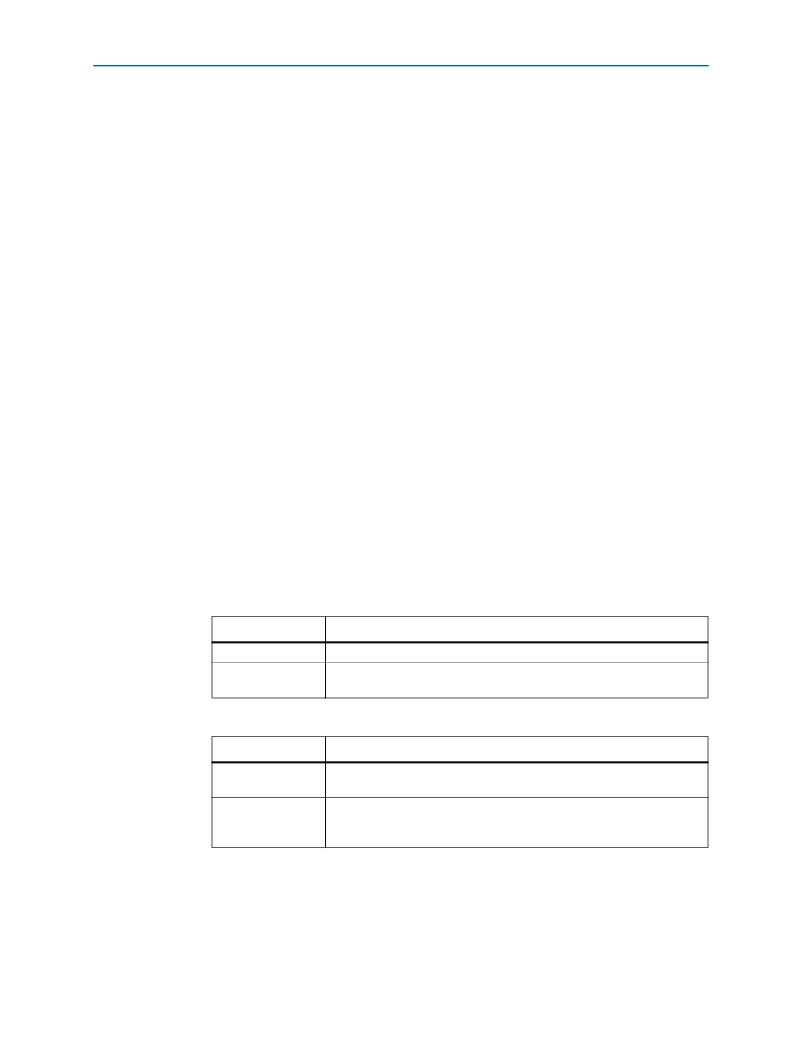

�Table� 3–9.� CRC� Type� Options�

�16-bit�

�32-bit�

�Option�

�Description�

�Generates� a� two-byte� CRC.� Adequate� for� packets� of� around� 1� KBytes� or�

�smaller.� This� is� the� default� algorithm� once� CRC� usage� has� been� enabled.�

�Generates� a� 4-byte� CRC.� Should� only� be� used� for� packets� larger� than� about�

�1� KBytes� or� when� extreme� protection� is� required,� because� it� is�

�resource-intensive.�

�January� 2014�

�Altera� Corporation�

�SerialLite� II� MegaCore� Function�

�User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBM28DRMN-S288 | CONN EDGECARD 56POS .156 EXTEND |

| RSM08DTKI-S288 | CONN EDGECARD 16POS .156 EXTEND |

| ECM06DTMD-S273 | CONN EDGECARD 12POS R/A .156 SLD |

| ECM06DTMN-S273 | CONN EDGECARD 12POS R/A .156 SLD |

| RBM12DCCI-S189 | CONN EDGECARD 24POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPR-SRAM/QDRII | 功能描述:开发软件 QDRII SRAM Control MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-SSIP | 功能描述:开发软件 Crypto Bundle BU Solution RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-TRIETHERNET | 功能描述:开发软件 Triple Speed Ethernt MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-TRIETHERNETF | 功能描述:开发软件 3x Spd Ethernet MAC MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IP-R-UNIV-CORE | 制造商:Brady Corporation 功能描述:UNIVERSAL RIBBON CORE; For Use With:Bradys IP Printer ;RoHS Compliant: NA |

发布紧急采购,3分钟左右您将得到回复。