- 您现在的位置:买卖IC网 > PDF目录16076 > IPR-SLITE2 (Altera)IP SERIALLITE II RENEW PDF资料下载

参数资料

| 型号: | IPR-SLITE2 |

| 厂商: | Altera |

| 文件页数: | 50/110页 |

| 文件大小: | 0K |

| 描述: | IP SERIALLITE II RENEW |

| 标准包装: | 1 |

| 系列: | * |

| 类型: | MegaCore |

| 功能: | SerialLite II 协议 |

| 许可证: | 续用许可证 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页当前第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页

�� �

�

�

�Chapter� 3:� Parameter� Settings�

�Transceiver� Configuration�

�■�

�■�

�■�

�3–27�

�Dynamic� reconfiguration� and� offset� cancellation� for� Arria� II� GX� devices,� refer� to�

��Dynamic� reconfiguration� and� offset� cancellation� for� Stratix� IV� devices,� refer� to� the�

��Dynamic� reconfiguration� and� using� the� Altera� Reconfiguration� Controller� for�

�Arria� V,� Cyclone� V,� and� Stratix� V� devices,� refer� to� the� Altera� Transceiver� PHY� IP� Core�

��ALTGX� Support� Signals�

�This� section� describes� the� ALTGX� support� signals,� which� are� only� present� on� variants�

�that� use� the� Arria� II� GX� and� Stratix� IV� integrated� PHY.� They� are� connected� directly� to�

�the� ALTGX� instance.� In� many� cases� these� signals� must� be� shared� with� ALTGX�

�instances� that� are� implemented� in� the� same� device.� The� following� signals� exist:�

�■�

�■�

�■�

�■�

�■�

�cal_blk_clk�

�reconfig_clk�

�reconfig_togxb�

�reconfig_fromgxb�

�gxb_powerdown�

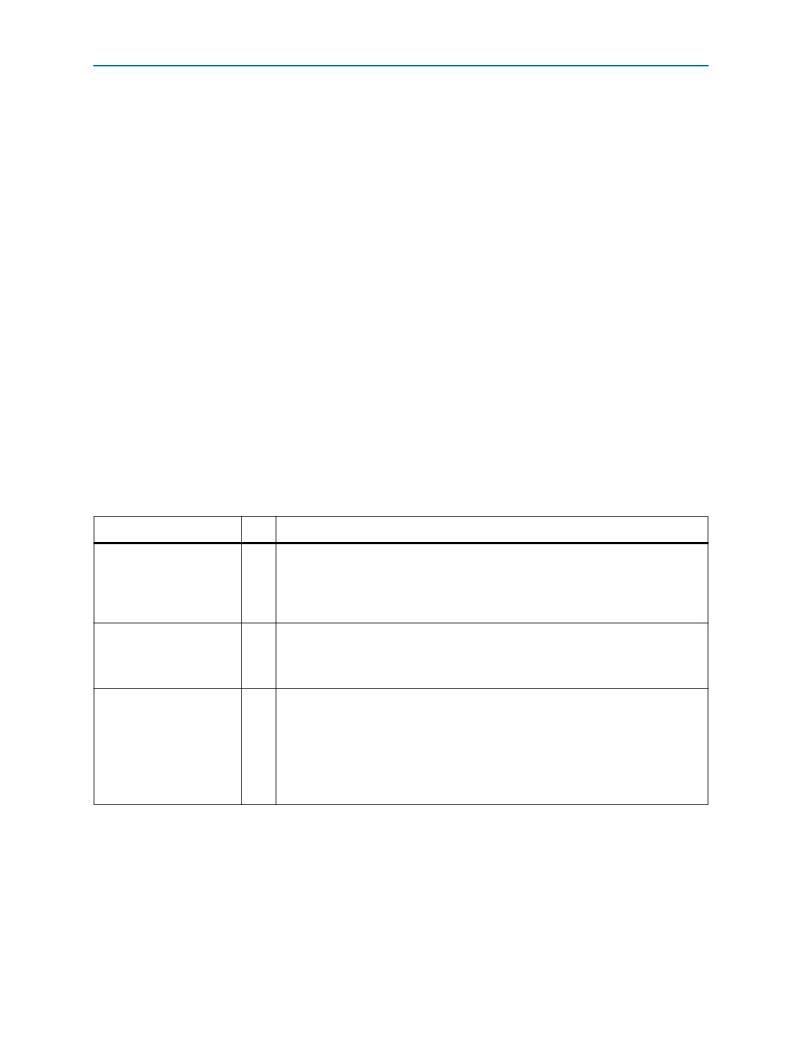

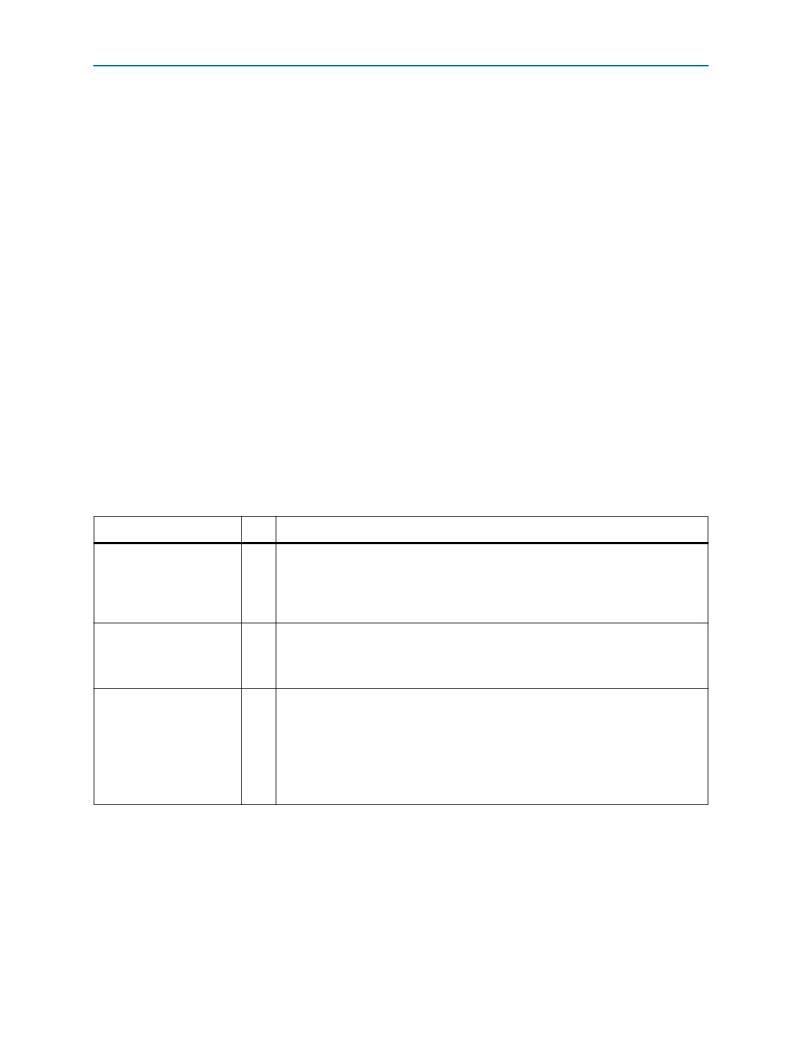

��Table� 3–11.� ALTGX� Support� Signals�

�Signal�

�cal_blk_clk�

�reconfig_clk�

�reconfig_togxb�

�I/O�

�I�

�I�

�I�

�Description�

�The� cal_blk_clk� input� signal� is� connected� to� the� ALTGX� calibration� block� clock�

�(� cal_blk_clk� )� input.� All� instances� of� ALTGX� in� the� same� device� must� have� their�

�cal_blk_clk� inputs� connected� to� the� same� signal� because� there� is� only� one�

�calibration� block� per� device.� This� input� should� be� connected� to� a� clock� operating� as�

�recommended� by� the� A� rr� ia� II� GX� Device� Ha� n� dbook� or� the� S� t� r� atix� IV� Device� Ha� n� dbook� .�

�The� reconfig_clk� input� signal� is� the� ALTGX� dynamic� reconfiguration� clock.� This�

�signal� must� be� connected� as� described� in� the� A� rr� ia� II� GX� Device� Ha� n� dbook� or� the�

�S� t� r� atix� IV� Device� Ha� n� dbook� if� the� ALTGX� dynamic� reconfiguration� block� is� used.�

�Otherwise,� this� signal� must� be� set� to� 1'b0� .�

�The� reconfig_togxb� [� N� :0]� input� signal� is� driven� from� an� external� dynamic�

�reconfiguration� block.� The� signal� supports� the� selection� of� multiple� transceiver�

�channels� for� dynamic� reconfiguration.� This� signal� must� be� connected� as� described� in�

�the� A� rr� ia� II� GX� Device� Ha� n� dbook� or� the� S� t� r� atix� IV� Device� Ha� n� dbook� if� the� external�

�dynamic� reconfiguration� block� is� used.� Otherwise,� you� must� set� this� signal� to�

�4'b0010� for� Arria� II� GX� and� Stratix� IV� devices.�

�N� value� is� 3� for� Arria� II� GX� and� Stratix� IV� devices.�

�January� 2014�

�Altera� Corporation�

�SerialLite� II� MegaCore� Function�

�User� Guide�

�相关PDF资料 |

PDF描述 |

|---|---|

| EBM28DRMN-S288 | CONN EDGECARD 56POS .156 EXTEND |

| RSM08DTKI-S288 | CONN EDGECARD 16POS .156 EXTEND |

| ECM06DTMD-S273 | CONN EDGECARD 12POS R/A .156 SLD |

| ECM06DTMN-S273 | CONN EDGECARD 12POS R/A .156 SLD |

| RBM12DCCI-S189 | CONN EDGECARD 24POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IPR-SRAM/QDRII | 功能描述:开发软件 QDRII SRAM Control MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-SSIP | 功能描述:开发软件 Crypto Bundle BU Solution RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-TRIETHERNET | 功能描述:开发软件 Triple Speed Ethernt MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IPR-TRIETHERNETF | 功能描述:开发软件 3x Spd Ethernet MAC MegaCore RENEWAL RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors |

| IP-R-UNIV-CORE | 制造商:Brady Corporation 功能描述:UNIVERSAL RIBBON CORE; For Use With:Bradys IP Printer ;RoHS Compliant: NA |

发布紧急采购,3分钟左右您将得到回复。